MOS-teknik 6502

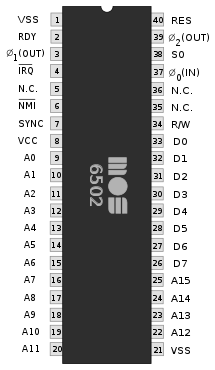

En MOS Technology 6502-processor i en DIP-40 plastförpackning. Den fyrsiffriga datumkoden anger att den gjordes under den 45:e veckan (november) 1985.

| |

| Allmän information | |

|---|---|

| Lanserades | 1975 |

| Vanliga tillverkare | |

| Prestanda | |

| Max. CPU klockfrekvens | 1 MHz till 3 MHz |

| Databredd | 8 bitar |

| Adressbredd | 16 bitar |

| Arkitektur och klassificering | |

| Instruktionsuppsättning | MOS 6502 |

| Instruktioner | 56 (55 ursprungligen) |

| Fysiska specifikationer | |

| Transistorer |

|

| Paket(er) |

|

| Historia | |

| Företrädare |

|

| Efterträdare | |

MOS Technology 6502 (uttalas typiskt "sixty-five-oh-two" eller "six-five-oh-two") är en 8-bitars mikroprocessor som designades av ett litet team ledd av Chuck Peddle för MOS Technology . Designteamet hade tidigare arbetat på Motorola på Motorola 6800 -projektet; 6502 är i grunden en förenklad, billigare och snabbare version av den designen.

När den introducerades 1975 var 6502 den billigaste mikroprocessorn på marknaden med stor marginal. Den sålde till en början för mindre än en sjättedel av kostnaden för konkurrerande konstruktioner från större företag, som 6800 eller Intel 8080 . Dess introduktion orsakade snabba prissänkningar på hela processormarknaden. Tillsammans med Zilog Z80 utlöste den en rad projekt som resulterade i hemdatorrevolutionen i början av 1980-talet .

Populära videospelskonsoler och hemdatorer från 1980-talet och början av 1990-talet, som Atari 2600 , Atari 8-bitarsfamiljen , Apple II , Nintendo Entertainment System , Commodore 64 , Atari Lynx , BBC Micro och andra, använder 6502 eller varianter av den grundläggande designen. Strax efter 6502:ans introduktion köptes MOS Technology direkt av Commodore International , som fortsatte att sälja mikroprocessorn och licenserna till andra tillverkare. I början av 6502:an köptes den på andra plats av Rockwell och Synertek och licensierades senare till andra företag.

1981 startade Western Design Center utvecklingen av en CMOS- version, 65C02 . Detta fortsätter att användas i stor utsträckning i inbyggda system , med uppskattade produktionsvolymer på hundratals miljoner.

Historia och användning

Ursprung från Motorola

6502 designades av många av samma ingenjörer som hade designat Motorola 6800 mikroprocessorfamiljen. Motorola startade 6800 mikroprocessorprojektet 1971 med Tom Bennett som huvudarkitekt. Chiplayouten började i slutet av 1972, de första 6800 markerna tillverkades i februari 1974 och hela familjen släpptes officiellt i november 1974. John Buchanan var designern av 6800-chippet och Rod Orgill, som senare gjorde 6501:an, hjälpte Buchanan med kretsanalyser och chiplayout. Bill Mensch började på Motorola i juni 1971 efter att ha tagit examen från University of Arizona (vid 26 års ålder). Hans första uppdrag var att hjälpa till med att definiera de perifera IC:erna för 6800-familjen och senare var han huvuddesignern av 6820 Peripheral Interface Adapter (PIA). Motorolas ingenjörer kunde köra analoga och digitala simuleringar på en IBM 370-165 stordator. Bennett anlitade Chuck Peddle 1973 för att utföra arkitektoniskt stödarbete på de 6800-familjens produkter som redan pågår. Han bidrog på många områden, inklusive designen av 6850 ACIA (seriellt gränssnitt).

Motorolas målkunder var etablerade elektronikföretag som Hewlett-Packard , Tektronix , TRW och Chrysler . I maj 1972 började Motorolas ingenjörer besöka utvalda kunder och dela detaljerna om deras föreslagna 8-bitars mikroprocessorsystem med ROM, RAM, parallella och seriella gränssnitt. I början av 1974 tillhandahöll de tekniska prover av chipsen så att kunderna kunde prototypa sina konstruktioner. Motorolas strategi för "total produktfamilj" fokuserade inte på priset på mikroprocessorn, utan på att minska kundens totala designkostnad. De erbjöd utvecklingsprogramvara på en tidsdelningsdator, felsökningssystemet "EXORciser", utbildning på plats och support för fältapplikationsingenjörer. Både Intel och Motorola hade initialt tillkännagett ett pris på 360 $ för en enskild mikroprocessor. Det faktiska priset för produktionskvantiteter var mycket lägre. Motorola erbjöd ett designkit innehållande 6800 med sex supportchips för $300.

Peddle, som skulle följa med säljarna på kundbesök, fann att kunderna blev avskräckta av de höga kostnaderna för mikroprocessorchips. Samtidigt resulterade dessa besök undantagslöst i att ingenjörerna som han presenterade producerade listor med nödvändiga instruktioner som var mycket mindre än "alla dessa fancy instruktioner" som hade inkluderats i 6800. Peddle och andra teammedlemmar började beskriva designen av en förbättrad funktion, reducerad mikroprocessor. Vid den tiden hade Motorolas nya tillverkningsanläggning för halvledartillverkning i Austin, Texas, svårt att producera MOS-chips, och mitten av 1974 var början på en årslång lågkonjunktur i halvledarindustrin. Dessutom var många av de i Mesa, Arizona, missnöjda med den kommande flyttningen till Austin, Texas .

Motorolas ledning för avdelningen för halvledarprodukter var överväldigad av problem och visade inget intresse för Peddles lågkostnadsmikroprocessorförslag. Så småningom fick Peddle ett officiellt brev om att han skulle sluta arbeta med systemet. Peddle svarade på ordern genom att informera Motorola om att brevet representerade en officiell förklaring om att "projektet övergavs", och som sådan var den immateriella egendom han hade utvecklat till den punkten nu hans. I en intervju från november 1975 instämde Motorolas styrelseordförande, Robert Galvin, slutligen om att Peddles koncept var bra och att divisionen missade en möjlighet, "Vi valde inte rätt ledare inom halvledarprodukter divisionen." Divisionen omorganiserades och ledningen ersattes. Den nya gruppens vicepresident John Welty sa: "Halvledarförsäljningsorganisationen förlorade sin känslighet för kundernas behov och kunde inte fatta snabba beslut."

MOS-teknik

Peddle började leta utanför Motorola efter en finansieringskälla för detta nya projekt. Han kontaktade först Mosteks vd LJ Sevin , men han avböjde. Sevin erkände senare att detta berodde på att han var rädd att Motorola skulle stämma dem.

Medan Peddle besökte Ford Motor Company på en av sina försäljningsresor nämnde Bob Johnson, senare chef för Fords motorautomationsdivision, att deras tidigare kollega John Paivinen hade flyttat till General Instrument och lärt sig själv halvledardesign. Paivinen bildade sedan MOS Technology i Valley Forge, Pennsylvania 1969 tillsammans med två andra chefer från General Instrument, Mort Jaffe och Don McLaughlin. Allen-Bradley , en leverantör av elektroniska komponenter och industriella kontroller, förvärvade en majoritetsintresse 1970. Företaget designade och tillverkade skräddarsydda IC:er för kunder och hade utvecklat en serie miniräknare.

Efter att Mosteks ansträngningar föll igenom, kontaktade Peddle Paivinen, som "direkt fick det". Den 19 augusti 1974 lämnade Chuck Peddle, Bill Mensch, Rod Orgill, Harry Bawcom, Ray Hirt, Terry Holdt och Wil Mathys Motorola för att gå med i MOS. Mike Janes anslöt senare. Av de sjutton chipdesignerna och layoutpersonerna i 6800-teamet var det åtta kvar. Målet med teamet var att designa och producera en lågkostnadsmikroprocessor för inbyggda applikationer och att rikta in sig på en så bred kundbas som möjligt. Detta skulle bara vara möjligt om mikroprocessorn var låg kostnad, och teamet satte prismålet till $5 i volym. Mensch sa senare att målet inte var själva processorpriset, utan att skapa en uppsättning chips som kunde säljas för $20 för att konkurrera med den nyligen introducerade Intel 4040 som såldes för $29 i en liknande komplett chipset.

Chips produceras genom att skriva ut flera kopior av chipdesignen på ytan av en "wafer" , en tunn skiva av mycket rent kisel. Mindre marker kan tryckas i större antal på samma wafer, vilket minskar deras relativa pris. Dessutom innehåller wafers alltid ett antal små fysiska defekter som är utspridda över ytan. Alla chip som skrivs ut på den platsen kommer att misslyckas och måste kasseras. Mindre marker betyder att varje enskild kopia är mindre sannolikt att skrivs ut på en defekt. Av båda dessa skäl är kostnaden för slutprodukten starkt beroende av storleken på chipdesignen.

De ursprungliga 6800-chipsen var avsedda att vara 180 mils × 180 mils (4,6 mm × 4,6 mm), men layouten blev klar med 212 mils × 212 mils (5,4 mm × 5,4 mm), eller en yta på 29,0 mm 2 . För den nya designen krävde kostnadsmålet ett storleksmål på 153 mils × 168 mils (3,9 mm × 4,3 mm) eller en yta på 16,6 mm 2 . Flera nya tekniker skulle behövas för att nå detta mål.

Flyttar till NMOS

Det var två betydande framsteg som kom på marknaden precis när 6502 designades som gav betydande kostnadsminskningar. Den första var övergången till utarmningsbelastning NMOS . 6800 använde en tidig NMOS-process som krävde tre matningsspänningar, men en av chipets egenskaper var en inbyggd spänningsfördubblare som gjorde att en enkel +5 V-matning kunde användas för +5, -5 och +12 V internt, i motsats till andra kretsar från eran som Intel 8080 som krävde tre separata matningsstift. Även om den här funktionen minskade komplexiteten i strömförsörjningen och stiftlayouten, krävde den fortfarande separata kraftskenor till de olika grindarna på chippet, vilket ökade komplexiteten och storleken. Genom att gå över till den nya utarmningslastdesignen var en enda +5 V-försörjning allt som behövdes, vilket eliminerade all denna komplexitet.

En ytterligare praktisk fördel var att klocksignalen för tidigare CPU:er måste vara tillräckligt stark för att överleva all förlust när den färdades genom kretsarna, vilket nästan alltid krävde ett separat externt chip som kunde leverera en kraftfull signal. Med de reducerade effektkraven från NMOS kunde klockan flyttas till chippet, vilket förenklar den övergripande datordesignen. Dessa förändringar reducerade avsevärt komplexiteten och kostnaden för att implementera ett komplett system.

En annan förändring som ägde rum var införandet av projektionsmaskering . Tidigare mönstrades chips på waferns yta genom att placera en mask på waferns yta och sedan skina ett starkt ljus på den. Maskerna plockade ofta upp små bitar av smuts eller fotoresist när de lyftes bort från chipet, vilket orsakade brister på dessa platser på eventuell efterföljande maskering. Med komplexa konstruktioner som CPU:er skulle 5 eller 6 sådana maskeringssteg användas, och chansen att åtminstone ett av dessa steg skulle introducera ett fel var mycket stor. I de flesta fall var 90 % av sådana konstruktioner felaktiga, vilket resulterade i en avkastning på 10 %. Priset på arbetsexemplen fick täcka produktionskostnaden för de 90 % som slängdes.

1973 introducerade Perkin-Elmer Micralign -systemet, som projicerade en bild av masken på wafern istället för att kräva direktkontakt. Masker plockade inte längre upp smuts från wafers och varade i storleksordningen 100 000 användningar snarare än 10. Detta eliminerade steg-till-steg-fel och de höga felfrekvensen som tidigare sågs på komplexa konstruktioner. Avkastningen på processorer hoppade omedelbart från 10 % till 60 eller 70 %. Detta innebar att priset på CPU:n sjönk ungefär lika mycket och mikroprocessorn blev plötsligt en handelsvara.

MOS Technologys befintliga tillverkningslinjer var baserade på den äldre PMOS-tekniken, de hade ännu inte börjat arbeta med NMOS när teamet kom. Paivinen lovade att ha en NMOS-linje igång och köra i tid för att börja produktionen av den nya CPU:n. Han infriade löftet, den nya linjen var klar i juni 1975.

Designanteckningar

Chuck Peddle, Rod Orgill och Wil Mathys designade den ursprungliga arkitekturen för de nya processorerna. En artikel från september 1975 i tidningen EDN ger denna sammanfattning av designen:

MOS Technology 650X-familjen representerar ett medvetet försök av åtta före detta Motorola-anställda som arbetade med utvecklingen av 6800-systemet för att lägga ut en del som skulle ersätta och överträffa 6800, men ändå sälja under den. Med fördelen av facit i hand om 6800-projektet, gjorde MOS Technology-teamet med Chuck Peddle i spetsen följande arkitektoniska förändringar i Motorolas CPU...

Den huvudsakliga förändringen i termer av chipstorlek var elimineringen av tri-state-drivrutinerna från adressbussutgångarna. En buss med tre tillstånd har tillstånd för "1", "0" och "hög impedans". Det sista tillståndet används för att tillåta andra enheter att komma åt bussen och används vanligtvis för multiprocessing , eller mer vanligt i dessa roller, för direkt minnesåtkomst (DMA). Även om den är användbar, är den här funktionen mycket dyr när det gäller on-chip-kretsar. 6502 tog helt enkelt bort denna funktion, i linje med dess design som en billig kontroller som används för specifika uppgifter och kommunicerar med enkla enheter. Peddle föreslog att alla som faktiskt behövde den här typen av åtkomst kunde implementera den med en enda 74158 .

Nästa stora skillnad var att förenkla registren. Till att börja med togs en av de två ackumulatorerna bort. Allmänna register som ackumulatorer måste nås av många delar av instruktionsavkodaren och kräver därför betydande mängder ledningar för att flytta data till och från deras lagring. Två ackumulatorer gör många kodningsuppgifter enklare, men kostar själva chipdesignen betydande komplexitet. Ytterligare besparingar gjordes genom att minska stackregistret från 16 till 8 bitar, vilket innebar att stacken bara kunde vara 256 byte lång, vilket räckte för dess avsedda roll som mikrokontroller. [ misslyckad verifiering ]

16-bitars IX- indexregistret delades i två och blev X och Y. Ännu viktigare, åtkomststilen ändrades; i 6800 hade IX en 16-bitars adress, som kompenserades av ett 8-bitars nummer som tillhandahölls med instruktionen, de två lades till för att producera den slutliga adressen. I 6502 (och de flesta andra samtida konstruktioner) lagrades 16-bitars basadressen i instruktionen och X eller Y lades till den.

Slutligen förenklades instruktionsuppsättningen, vilket frigjorde utrymme i dekodern och styrlogiken. Av de ursprungliga 72 instruktionerna i 6800, implementerades 56. Bland de borttagna fanns instruktioner som flyttade data mellan 6800:s två ackumulatorer, och flera greninstruktioner inspirerade av PDP- 11 , såsom möjligheten att direkt jämföra två numeriska värden. 6502 använde ett enklare system som hanterade jämförelser genom att utföra en subtraktion som satte de lämpliga flaggorna utan att spara resultatet, följt av en villkorlig greninstruktion som testade flaggorna.

Chipets design på hög nivå måste omvandlas till ritningar av transistorer och sammankopplingar. På MOS Technology var "layouten" en mycket manuell process som gjordes med färgpennor och velängpapper . Layouten bestod av tusentals polygonformer på sex olika ritningar; en för varje lager i tillverkningsprocessen. Med tanke på storleksgränserna måste hela chipdesignen ständigt övervägas. Mensch och Paivinen arbetade med instruktionsavkodaren medan Mensch, Peddle och Orgill arbetade med ALU och register. Ytterligare ett framsteg, utvecklat på en fest, var ett sätt att dela en del av de interna kablarna för att tillåta ALU att reduceras i storlek.

Trots deras bästa ansträngningar blev den slutliga designen 5 mil för bred. De första 6502 chipsen var 168 × 183 mils (4,3 × 4,7 mm), för en yta på 19,8 mm 2 . Den ursprungliga versionen av processorn hade ingen rotation right (ROR) förmåga, så instruktionen uteslöts från originaldokumentationen. Nästa iteration av designen krympte chipet och lade till möjligheten att rotera åt höger, och ROR inkluderades i den reviderade dokumentationen.

Vi presenterar 6501 och 6502

MOS skulle introducera två mikroprocessorer baserade på samma underliggande design: 6501 skulle anslutas till samma sockel som Motorola 6800, medan 6502 omarrangerade pinouten för att stödja en on-chip klockoscillator. Båda skulle fungera med andra stödchips designade för 6800. De skulle inte köra 6800-programvara eftersom de hade en annan instruktionsuppsättning, olika register och mestadels olika adresseringslägen. Rod Orgill var ansvarig för 6501-designen; han hade assisterat John Buchanan på Motorola på 6800:an. Bill Mensch gjorde 6502:an; han var konstruktören av 6820 Peripheral Interface Adapter (PIA) hos Motorola. Harry Bawcom, Mike Janes och Sydney-Anne Holt hjälpte till med layouten.

MOS Technologys mikroprocessorintroduktion skilde sig från den traditionella månadslånga produktlanseringen. Den första körningen av en ny integrerad krets används normalt för intern testning och delas med utvalda kunder som "ingenjörsprover". Dessa chips har ofta ett mindre konstruktionsfel eller två som kommer att åtgärdas innan produktionen påbörjas. Chuck Peddles mål var att sälja de första 6501- och 6502-markerna till deltagarna på WESCON-mässan i San Francisco som började den 16 september 1975. Peddle var en mycket effektiv talesman och MOS Technologys mikroprocessorer behandlades flitigt i fackpressen. En av de tidigaste var en helsidesartikel om mikroprocessorerna MCS6501 och MCS6502 i numret av Electronics magazine den 24 juli 1975. Berättelser gick också i EE Times (24 augusti 1975), EDN (20 september 1975), Electronic News (3 november 1975), Byte (november 1975) och Microcomputer Digest (november 1975). Annonser för 6501:an dök upp i flera publikationer första veckan i augusti 1975. 6501:an skulle vara till salu på Wescon för $20 styck. I september 1975 inkluderade annonserna både mikroprocessorerna 6501 och 6502. 6502 skulle bara kosta 25 USD (motsvarande 126 USD 2021).

När MOS Technology anlände till Wescon upptäckte de att utställare inte fick sälja något på mässgolvet. De hyrde MacArthur Suite på St. Francis Hotel och riktade kunderna dit för att köpa processorerna. I sviten förvarades processorerna i stora burkar för att antyda att chipsen var i produktion och lättillgängliga. Kunderna visste inte att den nedre halvan av varje burk innehöll icke-funktionella chips. Markerna var $20 och $25 medan dokumentationspaketet var ytterligare $10 . Användare uppmuntrades att göra fotokopior av dokumenten, ett billigt sätt för MOS Technology att distribuera produktinformation. De preliminära databladen listade bara 55 instruktioner exklusive Rotate Right (ROR)-instruktionen som inte stöddes på dessa tidiga marker. Granskningarna i Byte och EDN noterade avsaknaden av ROR-instruktionen. Nästa revidering av layouten fixade detta problem och databladet från maj 1976 listade 56 instruktioner. Peddle ville att alla intresserade ingenjörer och hobbyister skulle ha tillgång till chipsen och dokumentationen; andra halvledarföretag ville bara ha att göra med "seriösa" kunder. Signetics introducerade till exempel mikroprocessorn 2650 och dess annonser bad läsarna att skriva för information på företagets brevpapper.

| Stift | 6800 | 6501 | 6502 |

|---|---|---|---|

| 2 | Stanna | Redo | Redo |

| 3 | ∅1 (tum) | ∅1 (tum) | ∅1 (ut) |

| 5 | Giltig minnesadress | Giltig minnesadress | NC |

| 7 | Buss tillgänglig | Buss tillgänglig | SYNKRONISERA |

| 36 | Databussaktivering | Databussaktivering | NC |

| 37 | ∅2 (tum) | ∅2 (tum) | ∅0 (tum) |

| 38 | NC | NC | Ställ översvämningsflagga |

| 39 | Trestatskontroll | NC | ∅2 (ut) |

Motorola stämning

Introduktionen av 6501/6502 i tryck och på Wescon var en enorm framgång. Nackdelen var att den omfattande pressbevakningen fick Motorolas uppmärksamhet. I oktober 1975 sänkte Motorola priset på en enda 6800 mikroprocessor från 175 USD till 69 USD . Systemdesignsatsen på $300 reducerades till $150 och den kom nu med ett kretskort. Den 3 november 1975 begärde Motorola ett föreläggande i Federal Court för att stoppa MOS Technology från att tillverka och sälja mikroprocessorprodukter. De lämnade också in en stämningsansökan där de hävdade patentintrång och förskingring av affärshemligheter. Motorola hävdade att sju tidigare anställda gick med i MOS Technology för att skapa företagets mikroprocessorprodukter.

Motorola var ett miljardföretag med ett rimligt fall och dyra advokater. Den 30 oktober 1974 hade Motorola lämnat in ett flertal patentansökningar på mikroprocessorfamiljen och beviljades tjugofem patent. Den första var i juni 1976 och den andra var till Bill Mensch den 6 juli 1976 för 6820 PIA-chiplayouten. Dessa patent täckte 6800-bussen och hur de perifera chipsen samverkade med mikroprocessorn. Motorola började tillverka transistorer 1950 och hade en portfölj av halvledarpatent. Allen-Bradley bestämde sig för att inte bekämpa detta fall och sålde tillbaka sitt intresse för MOS Technology till grundarna. Fyra av de tidigare Motorola-ingenjörerna namngavs i kostymen: Chuck Peddle, Will Mathys, Bill Mensch och Rod Orgill. Alla utnämndes till uppfinnare i de 6800 patentansökningarna. Under upptäcktsprocessen upptäckte Motorola att en ingenjör, Mike Janes, hade ignorerat Peddles instruktioner och tagit med sina 6800 designdokument till MOS Technology. I mars 1976 höll det numera oberoende MOS Technology slut på pengar och var tvungen att lösa fallet. De gick med på att släppa 6501-processorn, betala Motorola 200 000 dollar och returnera de dokument som Motorola hävdade var konfidentiella. Båda företagen gick med på att korslicensiera mikroprocessorpatent. I maj sänkte Motorola priset på en enskild 6800-mikroprocessor till 35 USD . I november Commodore förvärvat MOS Technology.

Datorer och spel

Med juridiska problem bakom sig, var MOS fortfarande kvar med problemet med att få utvecklare att prova sin processor, vilket fick Chuck Peddle att designa enkortsdatorn MDT-650 ("mikrodatorutvecklingsterminal" ) . En annan grupp inom företaget designade KIM-1 , som såldes halvkomplett och kunde förvandlas till ett användbart system med tillägget av en tredje parts datorterminal och en kompakt kassettenhet. Även om den sålde bra till sin avsedda marknad, fann företaget att KIM-1 också sålde bra till hobbyister och pysslare. Det relaterade Rockwell AIM-65 kontroll-, tränings- och utvecklingssystemet gick också bra. Mjukvaran i AIM 65 var baserad på den i MDT. En annan ungefär liknande produkt var Synertek SYM-1 .

En av de första "offentliga" användningsområdena för designen var Apple I mikrodator , som introducerades 1976. 6502:an användes sedan i Commodore PET och Apple II , båda släpptes 1977. Den användes senare i Atari 8-bitars familje- och Acorn Atom- hemdatorer, BBC Micro , VIC-20 och andra mönster både för hemdatorer och företag, som Ohio Scientific och Oric . 6510 , en direkt efterföljare till 6502 med en digital I/O-port och en tri-state adressbuss, var CPU :n som användes i den bästsäljande Commodore 64 hemdatorn.

En annan viktig användning av 6500-familjen var i videospel. Den första som använde sig av processordesignen var 1977 års Atari VCS, senare omdöpt till Atari 2600 . VCS använde en 6502-variant som heter 6507 , som hade färre stift, så den kunde endast adressera 8 KB minne. Miljontals Atari-konsoler skulle säljas, var och en med en MOS-processor. En annan betydande användning var av Nintendo Entertainment System och Famicom. 6502:an som användes i NES var en andra källversion av Ricoh , ett partiellt system på ett chip , som saknade det binärkodade decimalläget men som lade till 22 minneskartade register och hårdvara för ljudgenerering, joypad-läsning och sprite lista DMA . Kallas 2A03 i NTSC- konsoler och 2A07 i PAL -konsoler (skillnaden är minnesdelarförhållandet och en uppslagstabell för ljudsamplingshastigheter), producerades denna processor exklusivt för Nintendo . Atari Lynx använde en 4 MHz-version av chipet, 65SC02 .

6502 eller varianter användes i alla Commodores diskettenheter för alla deras 8-bitars datorer, från PET-linjen till Commodore 128D, inklusive Commodore 64. 8-tums PET-enheter hade två 6502-processorer . Atari använde samma 6507 som används i Atari VCS för sina 810 och 1050 diskenheter som används för hela deras 8-bitars datorlinje, från 400/800 till XEGS.

På 1980-talet använde en populär elektroniktidning Elektor/Elektuur processorn i sitt mikroprocessorutvecklingskort Junior Computer .

- Hemdatorer och videospelskonsoler som använder 6502 eller dess varianter

Teknisk beskrivning

| 1 5 | 1 4 | 1 3 | 1 2 | 1 1 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | (bitposition) |

| Huvudregister | ||||||||||||||||

| A | En ackumulator | |||||||||||||||

| Indexregister | ||||||||||||||||

| X | X- index | |||||||||||||||

| Y | Y- index | |||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | SP | S tack P ointer | |||||||

| Programräknare | ||||||||||||||||

| PC | P rogramräknare _ _ | |||||||||||||||

| Statusregister | ||||||||||||||||

| N | V | - | B | D | jag | Z | C | P rocessor F lags | ||||||||

6502 är en liten 8-bitars processor med en 16-bitars adressbuss . De ursprungliga versionerna tillverkades med ett 8 µm processteknikchip med en formstorlek på 3,9 mm × 4,3 mm (annonserad som 153 mils × 168 mils ), för en total yta på 16,6 mm 2 .

Den interna logiken körs med samma hastighet som den externa klockfrekvensen, men trots de låga klockhastigheterna (vanligtvis i närheten av 1 till 2 MHz ), var 6502:ans prestanda konkurrenskraftig med andra samtida CPU:er som använde betydligt snabbare klockor. Detta beror delvis på en enkel tillståndsmaskin implementerad av kombinationslogik (klocklös) i större utsträckning än i många andra konstruktioner; tvåfasklockan (som ger två synkroniseringar per cykel) skulle därigenom kunna styra maskincykeln direkt. Typiska instruktioner kan ta hälften så många cykler att slutföra på 6502 som på modern design. Liksom de flesta enkla processorer av eran, är det dynamiska NMOS 6502-chippet inte sekvenserat av ett mikrokod- ROM [ förtydligande behövs ] utan använder en PLA (som upptog cirka 15 % av chipytan) för instruktionsavkodning och sekvensering. Som i de flesta 8-bitars mikroprocessorer gör chippet en viss begränsad överlappning av hämtning och exekvering.

Den låga klockfrekvensen modererade hastighetskravet för minne och kringutrustning anslutna till CPU:n, eftersom endast cirka 50 % av klockcykeln var tillgänglig för minnesåtkomst (på grund av den asynkrona designen varierade denna andel kraftigt mellan chipversioner). Detta var kritiskt i en tid då prisvärt minne hade åtkomsttider i intervallet 250–450 ns .

Eftersom chippet endast fick åtkomst till minnet under vissa delar av klockcykeln, och dessa cykler indikerades av PHI2-låg utklockningsstift, kunde andra chips i ett system komma åt minnet under de tider då 6502:an var avstängd från bussen. Detta var ibland känt som "dold åtkomst". Denna teknik användes flitigt av datorsystem; de skulle använda minne som kan komma åt vid 2 MHz, och sedan köra CPU:n på 1 MHz. Detta garanterade att CPU- och videohårdvaran kunde interfoliera sina åtkomster, med en total prestanda som matchade minnesenhetens. När snabbare minnen blev tillgängliga på 1980-talet kunde nyare maskiner köras med högre klockfrekvenser, som 2 MHz-processorn i BBC Micro , och fortfarande använda busdelningstekniker.

Register

Precis som sin föregångare, 6800, har 6502 väldigt få register . 6502:ans register inkluderar ett 8-bitars ackumulatorregister (A), två 8-bitars indexregister (X och Y), 7 processorstatusflaggabitar (P; från bit 7 till bit 0 är dessa negativa (N), spill ( V), reserverad , break (B), decimal (D), avbryta avbrott (I), noll (Z) och bär (C) flagga), en 8-bitars stackpekare (S) och en 16-bitars programräknare (PC). Detta kan jämföras med en typisk design från samma era, Z80 , som har åtta allmänna 8-bitarsregister, som kan kombineras till fyra 16-bitars. Z80 hade också en komplett uppsättning alternativa register, vilket gjorde totalt sexton allmänna register.

För att kompensera något för bristen på register, inkluderade 6502 ett nollsidigt adresseringsläge som använder en adressbyte i instruktionen istället för de två som behövs för att adressera hela 64 KB minne. Detta ger snabb åtkomst till de första 256 byten RAM genom att använda kortare instruktioner. Chuck Peddle har sagt i intervjuer att den specifika avsikten var att tillåta dessa första 256 byte RAM att användas som register. [ citat behövs ]

Stackadressutrymmet är kopplat till minnessidan $01 , dvs adressintervallet $0100 – $01FF ( 256 – 511 ). Mjukvaruåtkomst till stacken görs via fyra underförstådda instruktioner för adresseringsläge, vars funktioner är att trycka eller skjuta (dra) ackumulatorn eller processorstatusregistret. Samma stack används också för subrutinanrop via JSR (hoppa till subrutin) och RTS (return from subroutine) instruktioner och för avbrottshantering .

Adressering

Chipet använder index- och stackregistren effektivt med flera adresseringslägen , inklusive ett snabbt läge "direktsida" eller "nollsida", liknande det som finns på PDP-8 , som får åtkomst till minnesplatser från adresserna 0 till 255 med en enda 8-bitars adress (sparar den cykel som normalt krävs för att hämta adressens högordningsbyte)—koden för 6502 använder nollsidan ungefär som koden för andra processorer skulle använda register. På vissa 6502-baserade mikrodatorer med ett operativsystem operativsystemet det mesta av noll sida, vilket bara lämnar en handfull platser för användaren.

Adresseringslägen inkluderar även underförstådda (1-byte instruktioner); absolut (3 byte); indexerad absolut (3 byte); indexerad nollsida (2 byte); relativ (2 byte); ackumulator (1); indirekt,x och indirekt,y (2); och omedelbart (2). Absolut läge är ett allmänt läge. Greninstruktioner använder en signerad 8-bitars offset i förhållande till instruktionen efter grenen; det numeriska området −128..127 översätts därför till 128 byte bakåt och 127 byte framåt från instruktionen efter grenen (vilket är 126 byte bakåt och 129 byte framåt från början av greninstruktionen). Ackumulatorläget använder ackumulatorn som en effektiv adress och behöver inga operanddata . Omedelbart läge använder en 8-bitars bokstavlig operand.

Indirekt adressering

De indirekta lägena är användbara för arraybehandling och annan looping. Med 5/6-cykelns "(indirekt),y"-mod, adderas 8-bitars Y-registret till en 16-bitars basadress som läses från nollsida, som är lokaliserad av en enda byte som följer opkoden. Y-registret är därför ett indexregister i den meningen att det används för att hålla ett faktiskt index (till skillnad från X-registret i 6800, där en basadress var direkt lagrad och till vilken en omedelbar offset kunde läggas till). Att öka indexregistret för att gå arrayen bytevis tar bara två ytterligare cykler. Med den mindre ofta använda "(indirekt,x)"-moden hittas den effektiva adressen för operationen vid nollsidans adress som bildas genom att lägga till den andra byten av instruktionen till innehållet i X-registret. Genom att använda de indexerade lägena fungerar nollsidan effektivt som en uppsättning av upp till 128 ytterligare (men mycket långsamma) adressregister.

6502 kan utföra addition och subtraktion i binär eller binärkodad decimal . Att placera processorn i BCD-läge med SED- instruktionen (set D-flagga) resulterar i decimalaritmetik, där $99 + $01 skulle resultera i att $00 och bärflaggan (C) ställs in. I binärt läge ( CLD , rensa D-flagga), skulle samma operation resultera i att $9A och bärflaggan rensas. Förutom Atari BASIC användes BCD-läge sällan i hemdatorapplikationer.

Se Hej världen! artikel för ett enkelt men karakteristiskt exempel på 6502 assemblerspråk .

Instruktioner och opkoder

6502 instruktionsoperationskoder ( opcodes ) är 8 bitar långa och har den allmänna formen AAABBBCC, där AAA och CC definierar opkoden, och BBB definierar adresseringsläget.

Tänk till exempel på ORA- instruktionen, som utför ett bitvis ELLER på bitarna i ackumulatorn med ett annat värde. Instruktionens opcode är av formen 000bbb01, där bbb kan vara 010 för ett omedelbart lägesvärde (konstant), 001 för nollsidig fast adress, 011 för en absolut adress och så vidare.

Detta mönster är inte absolut, och det finns ett antal undantag. Däremot, där det är tillämpligt, gör det att man enkelt kan dekonstruera opcode-värden tillbaka till assembly-mnemonics för majoriteten av instruktionerna, och hantera kantfodral med specialkod.

Av de 256 möjliga opkoderna som är tillgängliga med hjälp av ett 8-bitarsmönster, använder originalet 6502 151 av dem, organiserade i 56 instruktioner med (möjligen) flera adresseringslägen . Beroende på instruktions- och adresseringsläget kan op-koden kräva noll, en eller två extra byte för operander. Därför varierar 6502 maskininstruktioner i längd från en till tre byte. Operanden lagras i 6502:ans vanliga lilla endian-format .

65C816 , 16-bitars CMOS- avkomling av 6502, stöder också 24-bitars adressering, vilket resulterar i att instruktioner sätts samman med tre-byte operander, också arrangerade i little-endian-format .

De återstående 105 opkoderna är odefinierade. I den ursprungliga designen användes inte instruktioner där de låga ordningens 4 bitar ( nibble ) var 3, 7, B eller F, vilket gav utrymme för framtida expansion. Likaså hade kolumnen $2x bara en enda post, LDX # konstant . De återstående 25 tomma platserna delades ut. Några av de tomma platserna användes i 65C02 för att tillhandahålla både nya instruktioner och variationer på befintliga med nya adresseringslägen. $Fx-instruktionerna lämnades till en början fria för att låta tredjepartsleverantörer lägga till sina egna instruktioner, men senare versioner av 65C02 standardiserade en uppsättning bitmanipuleringsinstruktioner utvecklade av Rockwell Semiconductor .

assembleringsspråk

En 6502- sammansättningsspråksats består av en instruktionsmnemonic med tre tecken följt av eventuella operander . Instruktioner som inte tar en separat operand utan riktar sig mot ett enda register baserat på adresseringsmoden kombinerar målregistret i instruktionsmnemoniken, så assemblern använder INX i motsats till INC X för att öka X-registret.

Instruktionstabell

| Opkodmatris för 6502-instruktionsuppsättningen | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Adresseringslägen: A – ackumulator, # – omedelbar, zpg – nollsida, abs – absolut, ind – indirekt, X – indexerad av X-register, Y – indexerad av Y-register, rel – relativ | ||||||||||||

| Hög napp | Lågt napp | |||||||||||

| 0 | 1 | 2 | 4 | 5 | 6 | 8 | 9 | A | C | D | E | |

| 0 | BRK | ORA ( ind ,X) | ORA zpg | ASL zpg | PHP | ORA # | ASL A | ORA abs | ASL abs | |||

| 1 | BPL rel | ORA ( ind ),Y | ORA zpg ,X | ASL zpg ,X | CLC | ORA abs ,Y | ORA abs ,X | ASL abs ,X | ||||

| 2 | JSR abs | AND ( ind ,X) | BIT zpg | OCH zpg | ROL zpg | PLP | OCH # | ROL A | BIT abs | OCH abs | ROL abs | |

| 3 | BMI rel | OCH ( ind ),Y | OCH zpg ,X | ROL zpg ,X | SEC | OCH abs ,Y | OCH abs ,X | ROL abs ,X | ||||

| 4 | RTI | EOR ( ind ,X) | EOR zpg | LSR zpg | PHA | EOR # | LSR A | JMP abs | EOR abs | LSR abs | ||

| 5 | BVC rel | EOR ( ind ),Y | EOR zpg ,X | LSR zpg ,X | CLI | EOR abs ,Y | EOR abs ,X | LSR abs ,X | ||||

| 6 | RTS | ADC ( ind ,X) | ADC zpg | ROR zpg | PLA | ADC # | ROR A | JMP ( ind ) | ADC abs | ROR abs | ||

| 7 | BVS rel | ADC ( ind ),Y | ADC zpg ,X | ROR zpg ,X | SEI | ADC abs ,Y | ADC abs ,X | ROR abs ,X | ||||

| 8 | STA ( ind ,X) | STY zpg | STA zpg | STX zpg | DEY | TXA | STY abs | STA abs | STX abs | |||

| 9 | BCC rel | STA ( ind ),Y | STY zpg ,X | STA zpg ,X | STX zpg ,Y | TYA | STA abs ,Y | TXS | STA abs ,X | |||

| A | LDY # | LDA ( ind ,X) | LDX # | LDY zpg | LDA zpg | LDX zpg | TAY | LDA # | BESKATTA | LDY abs | LDA abs | LDX abs |

| B | BCS rel | LDA ( ind ),Y | LDY zpg ,X | LDA zpg ,X | LDX zpg ,Y | CLV | LDA abs ,Y | TSX | LDY abs ,X | LDA abs ,X | LDX abs ,Y | |

| C | CPY # | CMP ( ind ,X) | CPY zpg | CMP zpg | DEC zpg | INY | CMP # | DEX | CPY abs | CMP abs | DEC abs | |

| D | BNE rel | CMP ( ind ),Y | CMP zpg ,X | DEC zpg ,X | CLD | CMP abs ,Y | CMP abs ,X | DEC abs ,X | ||||

| E | CPX # | SBC ( ind ,X) | CPX zpg | SBC zpg | INC zpg | INX | SBC # | NEJ | CPX abs | SBC abs | INC abs | |

| F | BEQ rel | SBC ( ind ),Y | SBC zpg ,X | INC zpg ,X | SED | SBC abs ,Y | SBC abs ,X | INC abs ,X | ||||

| Tomma opkoder (t.ex. F2 ) och alla opkoder vars låga nibbles är 3 , 7 , B och F är odefinierade i 6502-instruktionsuppsättningen. | ||||||||||||

Detaljerat beteende

Processorns ingång för icke-maskerbar avbrott (NMI) är kantkänslig , vilket innebär att avbrottet utlöses av signalens fallande flank snarare än dess nivå. Innebörden av denna funktion är att en trådbunden ELLER- avbrottskrets inte lätt stöds. Detta förhindrar dock också kapslade NMI-avbrott från att inträffa tills hårdvaran gör NMI-ingången inaktiv igen, ofta under kontroll av NMI- avbrottshanteraren .

Det samtidiga påståendet av NMI och IRQ (maskerbara) hårdvaruavbrottslinjer gör att IRQ ignoreras. Men om IRQ-linjen förblir hävdad efter service av NMI, kommer processorn omedelbart att svara på IRQ, eftersom IRQ är nivåkänslig . Således etablerades en sorts inbyggd avbrottsprioritet i 6502-designen.

B-flaggan sätts genom att 6502:an periodiskt samplar sin NMI-kantdetektors utgång och dess IRQ-ingång. IRQ-signalen som drivs lågt känns bara igen om IRQ:er tillåts av I-flaggan. Om på detta sätt en NMI-begäran eller (maskerbar) IRQ detekteras sätts B-flaggan till noll och får processorn att exekvera BRK-instruktionen nästa istället för att exekvera nästa instruktion baserat på programräknaren.

BRK-instruktionen skjuter sedan in processorstatusen till stacken, med B-flaggabiten inställd på noll. I slutet av dess exekvering återställer BRK-instruktionen B-flaggans värde till ett. Detta är det enda sättet B-flaggan kan modifieras. Om en annan instruktion än BRK-instruktionen trycker B-flaggan på stacken som en del av processorstatusen har B-flaggan alltid värdet ett.

En hög-till-låg-övergång på SO-ingångsstiftet kommer att ställa in processorns overflow-statusbit. Detta kan användas för snabb respons på extern hårdvara. kan en drivrutin för höghastighetsavfrågningsenhet polla hårdvaran en gång på bara tre cykler med hjälp av en Branch-on-oVerflow-Clear ( BVC )-instruktion som förgrenar sig till sig själv tills spill ställs in av en SO-fallande övergång. Commodore 1541 och andra Commodore- diskettenheter använder denna teknik för att upptäcka när serializern är redo att överföra ytterligare en byte med diskdata. Systemets hård- och mjukvarudesign måste säkerställa att en SO inte kommer att inträffa under aritmetisk bearbetning och störa beräkningar.

Variationer och derivator

Det finns många varianter av den ursprungliga NMOS 6502.

| Företag | Modell | Beskrivning |

|---|---|---|

| 6502 | Ett 1 MHz-chip som användes i KIM-1 och andra enkelkortsdatorer i mitten av 1970-talet. | |

| 6502A | Ett 1,5 MHz-chip som används i Asteroids Deluxe och vid 2 MHz, i BBC Micro | |

| 6502B | Version av 6502 som kan köras med en maximal hastighet på 3 MHz istället för 2 MHz. B användes i Apple III och, klockad till 1,79 MHz, tidiga Atari 8-bitars datorer . | |

| 6502C | Den "officiella" 6502C var en version av den ursprungliga 6502 som kunde köras på upp till 4 MHz. Inte att förväxla med SALLY, en anpassad 6502 designad för Atari (och ibland kallad "6502C") eller med den liknande namngivna 65C02 . |

|

| SALLY, C014806, "6502C" |

Anpassad 6502-variant designad för Atari, använd i senare Atari 8-bitars datorer och Atari 5200 och Atari 7800 konsoler. Har en HALT-signal på stift 35 och R/W-signalen på stift 36 (dessa stift är inte anslutna (N/C) på en standard 6502). Om du drar HALT lågt låses klockan och pausar processorn. Detta användes för att tillåta videokretsen direkt minnesåtkomst (DMA). Även om det ibland kallas "6502C" i Atari-dokumentationen, är detta inte detsamma som den "officiella" 6502C och själva chippet är aldrig märkt som sådant. |

|

| MOS | 6503 | Minskad minnesadresseringskapacitet (4 KB) och ingen RDY-ingång, i ett 28-stifts DIP-paket (med fas 1 (OUT), SYNC, redundanta Vss och SO-stift från 6502 också utelämnade). |

| MOS | 6504 | Minskad minnesadresseringskapacitet (8 KB), ingen NMI och ingen RDY-ingång, i ett 28-stifts DIP-paket (med fas 1 (OUT), SYNC, redundanta Vss och SO-stift för 6502 också utelämnade). |

| MOS | 6505 | Minskad minnesadresseringskapacitet (4 KB) och inget NMI, i ett 28-stifts DIP-paket (med fas 1 (OUT), SYNC, redundanta Vss och SO-stift från 6502 också utelämnade). |

| MOS | 6506 | Minskad minnesadresseringskapacitet (4 KB), ingen NMI och ingen RDY-ingång, men alla 3 klockstiften på 6502 (dvs en 2-fas utgångsklocka), i ett 28-stifts DIP-paket (med SYNC, redundant Vss, och SO-stiften på 6502 har också utelämnats). |

| MOS | 6507 | Minskad minnesadresseringsförmåga (8 KB) och inga avbrott, i ett 28-stifts DIP-paket (med fas 1 (OUT), SYNC, redundanta Vss och SO-stift från 6502 också utelämnade). Detta chip användes i Atari 2600- videospelsystemet. |

| MOS | 6508 | Har en inbyggd 8-bitars in-/utgångsport och 256 byte internt statiskt RAM-minne. |

| MOS | 6509 | Kan adressera upp till 1 MB RAM som 16 banker på 64 KB och användes i Commodore CBM-II- serien. |

| MOS | 6510 | Har en inbyggd 6-bitars programmerbar in-/utgångsport och användes i Commodore 64 . 8500 är faktiskt en HMOS-version av 6510 och ersatte den i senare versioner av C64. |

| MOS |

6512 6513 6514 6515 |

MOS Technology 6512, 6513, 6514 och 6515 är beroende av en extern klocka istället för att använda en intern klockgenerator som 650x (t.ex. 6502). Detta användes med fördel i vissa konstruktioner där klockorna kunde köras asymmetriskt, vilket ökade den totala CPU-prestandan. 6512 är en 6502 med en 2-fasig klockingång för en extern klockoscillator istället för en inbyggd klockoscillator. 6513, 6514 och 6515 är på liknande sätt ekvivalenta med (respektive) en 6503, 6504 och 6505 med samma 2-fas klockingång. 6512 användes i BBC Micro B+64 . |

| Ricoh | 2A03 | 6502-variant inklusive en ljudbehandlingsenhet men saknar BCD-läget, som används i Nintendo Entertainment System . |

| MOS |

6591 6592 |

System på ett chip designar som använder en komplett Atari 2600 i ett 48-stifts DIP-paket. |

| WDC | 65C02 |

CMOS- version av NMOS 6502 som designades av Bill Mensch från Western Design Center (WDC), med minskad strömförbrukning, stöd för mycket högre klockhastigheter, nya instruktioner, nya adresseringslägen för vissa befintliga instruktioner och korrigering av NMOS-fel, som JMP ($xxFF) bugg. |

| WDC | 65SC02 | WDC 65C02-variant utan individuella bitmanipuleringsoperationer (RMB, SMB, BBR och BBS). Denna kärna, som körs på 4 MHz, användes i Atari Lynx huvudsystem IC. |

| CSG, MOS | 65CE02 | CMOS-variant utvecklad av Commodore Semiconductor Group (CSG), tidigare MOS Technology. |

| Rockwell |

R6511Q R6500/11, R6500/12, R6500/15 " One-Chip mikrodatorer " |

Förbättrade versioner av den 6502-baserade processorn, inklusive individuella bitmanipuleringsoperationer (RMB, SMB, BBR och BBS), on-chip 192 byte nollsidig RAM, UART , etc. |

| Rockwell |

R65F11 R65F12 |

Rockwell R65F11 (introducerades 1983) och den senare R65F12 är förbättrade versioner av den 6502-baserade processorn, inklusive individuella bitmanipuleringsoperationer (RMB, SMB, BBR och BBS), nollsidigt RAM på chipet, on-chip Forth kärn-ROM, en UART, etc. |

| GTE | G65SC102 | Programvara som är kompatibel med 65C02, men har en något annorlunda pinout och oscillatorkrets. BBC Master Turbo inkluderade 4 MHz-versionen av denna CPU på ett samprocessorkort, som också kunde köpas separat och läggas till Master 128. |

| Rockwell |

R65C00 R65C21 R65C29 |

R65C00, R65C21 och R65C29 har två förbättrade CMOS 6502 i ett enda chip, och R65C00 och R65C21 innehöll dessutom 2 KB maskprogrammerbart ROM. |

| CM630 | En 1 MHz östblocksklon av 6502 och användes i Pravetz 8A och 8C, bulgariska kloner av Apple //- serien. | |

| MOS |

7501 8501 |

6510 (en förbättrad 6502) varianter, introducerade 1984. De utökade antalet I/O-portstift från 6 till 7, men utelämnade stift för icke-maskerbar avbrott och klockutgång. Används i Commodores C-16 , C-116 och Plus/4- datorer. Den största skillnaden mellan 7501 och 8501 processorer är att 7501 tillverkades med HMOS -1-processen och 8501 med HMOS-2. |

| MOS | 8500 | Introducerades 1985 som en HMOS- version av 6510 (som i sin tur är baserad på 6502). Förutom processmodifieringen är 8500 praktiskt taget identisk med NMOS -versionen av 6510. Den ersatte 6510 i senare versioner av Commodore 64 . |

| MOS | 8502 | Designad av MOS Technology och används i Commodore 128 . Baserat på MOS 6510 som användes i Commodore 64 kunde 8502 köras med dubbel klockfrekvens av 6510. 8502-familjen inkluderar även MOS 7501, 8500 och 8501. |

| Hudson mjuk | HuC6280 | Japanska videospelsföretaget Hudson Softs förbättrade version av WDC 65C02. Tillverkad för dem av Seiko Epson och NEC för SuperGrafx . Den mest anmärkningsvärda produkten som använder HuC6280 är NEC:s TurboGrafx-16-spelkonsol. |

16-bitars derivator

Western Design Center designade och producerar för närvarande WDC 65C816 S-processorn, en 16-bitars, statisk kärna efterföljare till 65C02 . W65C816S är en nyare variant av 65C816, som är kärnan i Apple IIGS -datorn och är grunden för Ricoh 5A22- processorn som driver Super Nintendo Entertainment System . W65C816S innehåller mindre förbättringar jämfört med 65C816 som gör att det nyare chippet inte är en exakt hårdvarukompatibel ersättning för det tidigare. Bland dessa förbättringar fanns konvertering till en statisk kärna, vilket gör det möjligt att stoppa klockan i båda faserna utan att registren förlorar data. Tillgänglig via elektronikdistributörer, från och med mars 2020, är W65C816S officiellt klassad för 14 MHz-drift.

Western Design Center designade och producerade också 65C802 , som var en 65C816-kärna med ett 64-kilobyte adressutrymme i ett 65(C)02-stiftkompatibelt paket. 65C802 skulle kunna eftermonteras på ett 6502-kort och skulle fungera som en 65C02 vid uppstart och fungera i "emuleringsläge". Liksom med 65C816, skulle en två-instruktionssekvens växla 65C802 till "native mode"-drift, exponera dess 16-bitars ackumulator och indexregister och andra 65C816 funktioner. 65C802 användes inte i stor utsträckning och produktionen avslutades.

Exempelkod

Följande 6502 assembly- språkkällkod är för en subrutin som heter TOLOWER , som kopierar en noll-terminerad teckensträng från en plats till en annan, och konverterar stora bokstäver till gemener. Strängen som kopieras är "källan", och strängen som den konverterade källan lagras i är "destinationen".

41

0608

0080 0080 00 04 0082 00 05 0600 0600 A0 00 0602 B1 80 0604 F0 11 0606 C9 41 0608 90 06 060 A C9 5 B

060C B0 02

060E 09 20

0610 91 82

0612 C8

0613 D0 ED

0616 60

0617 91 82

0619 18

061A 60

061B

|

; TOLL: ; ; Konvertera en noll-terminerad teckensträng till små bokstäver. ; Maximal stränglängd är 255 tecken plus nolltermen- ; inator. ; ; Parametrar: ; ; SRC – Källsträngsadress ; DST – Destinationssträngadress ; ORG $0080 ; SRC .WORD $0400 ;källa strängpekare DST .WORD $0500 ;destinationssträngpekare ; ORG $0600 ;exekveringsstartadress ; TOLOWER LDY # $00 ;startindex

; LOOP LDA ( SRC ), Y ;get from source string BEQ DONE ;end of string ; CMP # 'A' ;om lägre än UC-alfabetet... BCC SKIP ;kopiera oförändrad ; CMP # 'Z' + 1 ;om det är större än UC-alfabetet... BCS SKIP ;kopiera oförändrat ; ORA # %00100000 ;konvertera till gemener ; SKIP STA ( DST ), Y ;lagra till destinationssträng INY ;bump index BNE LOOP ;nästa tecken ; ; OBS: Om Y radbryts kommer destinationssträngen att lämnas i en odefinierad ; stat. Vi ställer in bär för att indikera detta för den anropande funktionen. ; SEC ;rapportera strängen för lång fel &... RTS ;återvänd till den som ringer ; DONE STA ( DST ), Y ;terminate destination string CLC ;rapport omvandling slutförd &... RTS ;återvänd till den som ringer ; .SLUTET

|

Buggar och egenheter

6502:an hade flera buggar och egenheter, som man måste ta hänsyn till när man programmerar den:

- De tidigaste versionerna av 6502, som de som levererades med vissa KIM-1 -datorer, hade ingen ROR -instruktion (rotera åt höger minne eller ackumulator). Driften av ROR i dessa chips är i praktiken en ASL-instruktion (arithmetic shift left) som inte påverkar bärbiten i statusregistret. MOS lämnade instruktionen helt och hållet ur chipdokumentationen och lovade att ROR skulle dyka upp på 6502 chips från och med 1976. Den stora majoriteten av 6502 chips som finns idag uppvisar inte denna egenhet.

- NMOS 6502 - familjen har en mängd odokumenterade instruktioner , som varierar från en chiptillverkare till en annan. 6502-instruktionsavkodningen är implementerad i en fast ansluten logikmatris (liknande en programmerbar logikmatris ) som endast är definierad för 151 av de 256 tillgängliga opkoderna . De återstående 105 utlöser konstiga och ibland svårförutsägbara åtgärder, som att krascha processorn, utföra två giltiga instruktioner i följd, utföra konstiga blandningar av två instruktioner eller helt enkelt inte göra någonting alls. Eastern House Software utvecklade "Trap65", en enhet som kopplades mellan processorn och dess sockel för att konvertera (fälla) oimplementerade opkoder till BRK -instruktioner (programavbrott). [ citat behövs ] Vissa programmerare använde denna funktion för att utöka 6502-instruktionsuppsättningen genom att tillhandahålla funktionalitet för de oimplementerade opkoderna med specialskriven programvara som fångas upp av BRK-instruktionens 0xFFFE-vektor. Alla de odefinierade opkoderna har ersatts med NOP- instruktioner i 65C02 , en förbättrad CMOS- version av 6502, men med varierande bytestorlekar och exekveringstider. I 65C802/65C816 utför alla 256 opkoder definierade operationer.

- 6502:ans indirekta hoppinstruktion för minne ,

JMP (<adress>),är delvis trasig. Om <adress> är hex xxFF (dvs vilket ord som helst som slutar på FF ), kommer processorn inte att hoppa till adressen lagrad i xxFF ochxxFF+1som förväntat, utan snarare den som definieras av xxFF och xx00 (till exempelJMP ( $10FF)skulle hoppa till adressen lagrad i 10FF och 1000, istället för den som lagras i 10FF och 1100). Denna defekt fortsatte genom hela NMOS-linjen, men korrigerades i CMOS-derivaten. - Den NMOS 6502 indexerade adresseringen över sidgränserna kommer att göra en extra läsning av en ogiltig adress. Den här egenskapen kan orsaka slumpmässiga problem genom att komma åt hårdvara som verkar på en läsning, såsom att rensa timer eller IRQ-flaggor, skicka en I/O-handskakning, etc. Denna defekt fortsatte genom hela NMOS-linjen, men korrigerades i CMOS-derivaten, i som processorn gör en extra läsning av den sista instruktionsbyten.

- 6502 läs–ändra–skrivinstruktionerna utför en läs- och två skrivcykler. Först skrivs den omodifierade datan som lästes tillbaka, och sedan skrivs den modifierade datan. Denna egenskap kan orsaka problem genom att två gånger få åtkomst till hårdvara som verkar på en skrivning. Denna anomali fortsatte genom hela NMOS-linjen, men fixades i CMOS-derivaten, där processorn gör två läs- och en skrivcykel. Defensiv programmering kommer i allmänhet att undvika detta problem genom att inte exekvera läs/ändra/skrivinstruktioner på hårdvaruregister.

- Statusflaggorna N (resultat negativt), V (teckenbitspill) och Z (resultat noll) är i allmänhet meningslösa när man utför aritmetiska operationer medan processorn är i BCD- mod, eftersom dessa flaggor reflekterar det binära resultatet, inte BCD. Denna begränsning togs bort i CMOS-derivaten. Därför kan den här funktionen användas för att skilja en CMOS-processor från en NMOS-version.

- Om 6502 råkar vara i BCD-läge när ett hårdvaruavbrott inträffar, kommer den inte att återgå till binärt läge. Denna egenskap kan resultera i oklara buggar i avbrottstjänstrutinen om den inte lyckas rensa BCD-läget innan några aritmetiska operationer utförs. Till exempel Commodore 64 :s KERNAL inte denna processorkarakteristik korrekt, vilket kräver att IRQ: er inaktiveras eller återvektors under BCD-matematikoperationer. Detta problem behandlades också i CMOS-derivaten.

- 6502-instruktionsuppsättningen innehåller BRK (op-kod $00), vilket tekniskt sett är ett mjukvaruavbrott (liknar till sin anda SWI-mnemoniken för Motorola 6800 och ARM -processorerna). BRK används oftast för att avbryta programexekveringen och starta en maskinspråksmonitor för testning och felsökning under mjukvaruutveckling. BRK kan också användas för att dirigera programexekvering med hjälp av en enkel hopptabell (analogt med det sätt på vilket Intel 8086 och derivator hanterar programvaruavbrott efter nummer). Men om ett hårdvaruavbrott inträffar när processorn hämtar en BRK-instruktion, kommer NMOS-versionen av processorn att misslyckas med att exekvera BRK och istället fortsätta som om bara ett hårdvaruavbrott hade inträffat. Detta fel korrigerades i CMOS-implementeringen av processorn.

- När JSR (hoppa till subrutin) och RTS (retur från subrutin) instruktioner utförs, är returadressen som skickas till stacken av JSR den för den sista byten av JSR-operanden (det vill säga den mest signifikanta byten i subrutinadressen), istället för adressen till följande instruktion. Detta beror på att själva kopieringen (från programräknare till stack och sedan omvänt) sker före den automatiska ökningen av programräknaren som sker i slutet av varje instruktion. Denna egenskap skulle förbli obemärkt om inte koden undersökte returadressen för att hämta parametrar i kodströmmen (ett 6502 programmeringsspråk som dokumenterats i ProDOS 8 Technical Reference Manual ). Det är fortfarande ett kännetecken för 6502 derivat till denna dag.

- Läsåtkomsten för CPU:n kan fördröjas genom att tillfälligt ställa in RDY-stiftet till lågt. Emellertid, under skrivåtkomst, vilket kan ta upp till tre klockcykler för en BRK-instruktion, kommer CPU:n att stanna endast i nästa läscykel. Denna egenhet korrigerades i CMOS-derivaten och även i 6510 och dess varianter.

Se även

- Lista över 6502 montörer

- MOS Technology 6502-baserade hemdatorer

- Transistorantal

- Apple II acceleratorer

- cc65 – 6502 makro assembler och C kompilator

Anteckningar

Citat

Bibliografi

- Peddle, Chuck (12 juni 2014). "Oral History of Chuck Peddle" (Intervju). Intervjuad av Doug Fairbairn och Stephen Diamond. Arkiverad från originalet 2021-11-18.

- Bagnall, Brian (2010). Commodore, ett företag på kanten (2:a uppl.). Winnipeg, Manitoba: Variant Press. ISBN 978-0-9738649-6-0 .

- Bennett, Thomas; Ekiss, John; Lattin, William (Bill); Lavell, Jeff (28 mars 2008). "Motorola 6800 Oral History Panel" (PDF) (Intervju). Intervjuad av David Laws.

- Cushman, Robert H. (20 september 1975). "2-1/2 generations μP:s -$10 delar som fungerar som low-end mini" (PDF) . EDN . Boston: Cahners Publishing. 20 (17): 36–42. Arkiverad från originalet (PDF) den 24 april 2016.

- Intervju med William Mensch Stanford and the Silicon Valley Project, 9 oktober 1995. Avskrift

Vidare läsning

- Datablad och manualer

- 6500-seriens datablad ; MOS-teknik; 12 sidor; 1976.

- 6500-seriens maskinvaruhandbok ; 2:a upplagan; MOS-teknik; 182 sidor; 1976.

- 6500-seriens programmeringsmanual ; 2:a upplagan; MOS-teknik; 262 sidor; 1976.

- Böcker

- 6502 Applications Book ; 1:a upplagan; Rodnay Zaks ; Sybex; 281 sidor; 1979; ISBN 978-0895880154 . (arkiv)

- 6502 Assembly Language Programmering ; 2:a upplagan; Lance Leventhal; Osborne/McGraw-Hill; 650 sidor; 1986; ISBN 978-0078812163 . (arkiv)

- 6502 Assembly Language Subroutines ; 1:a upplagan; Lance Leventhal och Winthrop Saville; Osborne/McGraw-Hill; 550 sidor; 1982; ISBN 978-0931988592 . (arkiv)

- 6502 Spel ; 1:a upplagan; Rodnay Zaks; Sybex; 292 sidor; 1980; ISBN 978-0895880222 . (arkiv)

- 6502 Användarmanual ; 1:a upplagan; Joseph Carr; Vila på; 288 sidor; 1984; ISBN 978-0835970020 . (arkiv)

- Avancerad 6502-programmering ; 1:a upplagan; Rodnay Zaks; John Wiley & Sons; 292 sidor; 1982; ISBN 978-0895880895 . (arkiv)

- Maskinspråk för nybörjare – Persondator Maskinspråksprogrammering för Atari-, VIC-, Apple-, C64- och PET-datorer ; 1:a upplagan; Richard Mansfield; Beräkna! Publikationer; 350 sidor; 1983; ISBN 978-0942386110 . (arkiv)

- Programmering av 6502 ; 4:e upplagan; Rodnay Zaks; Sybex; 408 sidor; 1983; ISBN 978-0895881359 . (arkiv)

- Programmering av 65816 – inklusive 6502, 65C02 , 65802 ; 1:a upplagan; David Eyes och Ron Lichty; Prentice Hall; 636 sidor; 1986; ISBN 978-0893037895 . (arkiv)

- Mikroprocessorer och Assembly Language ; turkiska; 7:e upplagan; Nurettin Topaloglu; Seckin Yayinevi; 328 sidor; 2021; ISBN 978-975-02-6663-8 .

- Referenskort

- 6502 Microprocessor Instant Reference Card ; James Lewis; Micro Logic; 2 sidor; 1980. (arkiv)

externa länkar

- 6502.org – 6502 mikroprocessorresursen – arkiv

- The Rise of MOS Technology & The 6502 – Commodore-arkiv

- 650x information – Kortfattad beskrivning, bilder av MOS och andra källchips; på cpu-collection.de

- mdfs.net – 6502 instruktionsuppsättning

- Smart, Eric. "6502 – den första RISC µP" . Arkiverad från originalet den 24 maj 2012.

- Harrod, Dennette A. (oktober 1980). "6502 får mikroprogrammerbara instruktioner" . Byte . Vol. 5, nr. 10. McGraw Hill . s. 282–285. ISSN 0360-5280 . Arkiverad från originalet 2006-05-25 . Hämtad 2006-05-14 .

- Simulatorer, emulatorer

- Online 6502-kompatibel assembler och emulator, skriven i JavaScript Arkiverad 2011-02-08 på Wayback Machine

- Lista över 6502 mjukvaruemulatorer – Zophar's Domain

- 6502 simulator för Windows – Atari Gaming Headquarters

- Visual Transistor-nivå Simulering av 6502 CPU

- MCL65 6502 CPU-kärna, C-kod på GitHub – MicroCore Labs

- Brädor

- Grants 7/8-chip 6502-kort

- 6502 mikroprocessor utbildningstavla Arkiverad 2019-07-14 på Wayback Machine

- Bygg din egen KIM-1 träningstavla – se KIM-1

- 6502 hemdator på GitHub

- PE6502 enkelkortsdator Arkiverad 2020-05-03 på Wayback Machine

- BE6502 enkelkortsdator på GitHub – baserad på Ben Eater-videor

- FPGA

- cpu6502_tc 6502 CPU-kärna – VHDL-källkod – OpenCores

- ag_6502 6502 CPU-kärna – Verilog-källkod – OpenCores

- M65C02 65C02 CPU-kärna – Verilog-källkod – OpenCores

- MCL65 6502 CPU-kärna på GitHub – Verilog – MicroCore Labs