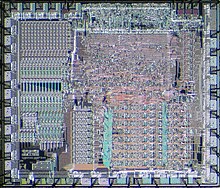

Signetics 2650

Signetics 2650AN

| |

| Allmän information | |

|---|---|

| Lanserades | 1975 |

| Vanliga tillverkare | |

| Prestanda | |

| Max. CPU klockfrekvens | 1,2 MHz |

| Databredd | 8 |

| Adressbredd | 15 |

| Fysiska specifikationer | |

| Paket(er) |

|

Signetics 2650 var en 8-bitars mikroprocessor som introducerades i juli 1975. Enligt Adam Osbornes bok An Introduction to Microprocessors Vol 2: Some Real Products var den "den mest minidatorliknande " av de mikroprocessorer som fanns på den tiden. En kombination av saknade funktioner och udda minnesåtkomst begränsade dess dragningskraft, och systemet såg lite användning på marknaden.

Utveckling

1972 anställde Signetics Jack Curtis John Kessler från IBM för att leda utformningen av en ny enchips-CPU avsedd att konkurrera med minidatorsystem . Kessler valde IBM 1130 som modell för den nya designen. 1130, som släpptes 1965, var en 16-bitars minidator som delade många designfunktioner med andra minis av eran.

Medan Kessler designade arkitekturen, lade Kent Andreas ut processorn med hjälp av en nyligen utvecklad jonimplantation NMOS -process. I motsats till den mycket vanligare PMOS- processen på eran, använde NMOS mindre ström och avledde mindre värme. Detta gjorde att chippet kunde köras med högre hastigheter än PMOS CPU-designer, och de första 2650:erna körde med samma hastighet på 1,25 MHz som de samtida modellerna av 1130.

När den designades 1972 var 2650 bland de mest avancerade designerna på marknaden, och överträffade enkelt och överträffade Intel 4004 och 8008 från samma tid. Trots detta släpptes designen inte till produktion. Vid den tiden var Signetics starkt involverad i Dolby Laboratories , och utvecklade integrerade kretsar som implementerade Dolbys serie av brusreduceringssystem . Tillverkningen av 2650 trycktes tillbaka, och processorn introducerades inte formellt förrän i juli 1975. År 1975 hade flera nya processorer introducerats, designade från början för att vara 8-bitarsmaskiner snarare än att efterlikna en äldre design, och 2650:s fördelar var inte längre lika övertygande.

1975 köpte Philips Signetics, och från den punkten kan versioner av 2650 hittas med både Signetics eller Philips varumärke.

I mars 1976 nådde Signetics ett andrahandsavtal med Advanced Memory Systems (AMS). På den tiden var de flesta CPU-företag väldigt små och ingen skulle köpa en design från ett företag som kunde gå i konkurs. Second-sourcing var en viktig garanti för att designen skulle förbli tillgänglig i detta fall. AMS fungerade redan som en andra källa för RCA 1802 , en avancerad CMOS- design, och NMOS 2650 sågs som ett användbart komplement som inte direkt skulle konkurrera med 1802. Tyvärr köptes AMS i november av Intersil , som hade deras egen Intersil 6100 , en enkelchipsversion av PDP-8 mini. Intersil lade ner produktionen av 2650.

Signetics försökte igen med National Semiconductor 1977, som planerade att introducera versioner under årets sista kvartal. Av okänd anledning verkar detta aldrig ha hänt, och endast ett enda exempel på en NS-version, från Frankrike, har någonsin hittats.

Signetics fortsatte utvecklingen av 2650:an och introducerade två nya modeller 1977. 2650A var en omarbetad version av den ursprungliga layouten avsedd att förbättra avkastningen och därmed minska kostnaderna. Hastigheten förblev oförändrad på 1,25 MHz för basmodellen och 2 MHz för -1-versionerna. 2650B var baserad på A, lade till ett antal nya instruktioner och förbättrade prestandan för ett antal befintliga instruktioner.

Beskrivning

| 1 4 | 1 3 | 1 2 | 1 1 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 | (bitposition) |

|

Alternativa register för allmänna ändamål |

|||||||||||||||

| REG3' | |||||||||||||||

| REG2' | |||||||||||||||

| REG1' | |||||||||||||||

|

Huvudregister för allmänna ändamål |

|||||||||||||||

| REG3 | |||||||||||||||

| REG2 | |||||||||||||||

| REG1 | |||||||||||||||

| REG0 | |||||||||||||||

|

Instruktion Adressregister |

|||||||||||||||

| Sida | |||||||||||||||

|

Subrutin returadressstack |

|||||||||||||||

| S0 | |||||||||||||||

| S1 | |||||||||||||||

| S2 | |||||||||||||||

| S2 | |||||||||||||||

| S4 | |||||||||||||||

| S5 | |||||||||||||||

| S6 | |||||||||||||||

| S7 | |||||||||||||||

| Programstatusord | |||||||||||||||

| S | F | II | Stack Ptr | PSU | |||||||||||

| CC | ID | RS | toalett | OV | CENTIMETER | C | PSL | ||||||||

Den övergripande designen av 2650 baserades på IBM 1130 . Som sådan har 2650 ett antal funktioner som var vanliga på 1960-talets minidatorer , men som sällan hittades på nydesignade mikroprocessorer från 1970-talet. Bland dessa fanns till exempel statusbitar som användes för att spåra statusen för in-/utgångsenheter , vilket gör det enklare att skriva gränssnittskod. En annan miniliknande funktion var dess användning av vektoriserade avbrott , som gjorde det möjligt för enheter att anropa den korrekta avbrottshanterarkoden genom att placera dess minnesplats på databussen och sedan tvinga fram ett avbrott. Detta undviker behovet av att skriva en centraliserad avbrottshanterare som läser ytterligare data från bussen, bestämmer vilken enhetsdrivrutin som anropas och sedan anropar den; 2650 kan hoppa direkt till rätt kod, eventuellt lagrad på själva enheten.

Liksom 1130, var 2650:s processorregister uppdelade i uppsättningar, med ett enda globalt register R0 som användes som ackumulator , och två uppsättningar av tre indexregister , båda benämnda R1, R2 och R3, för totalt sju register. När som helst var en av de två uppsättningarna av index synliga för CPU:n. Vilken uppsättning som var synlig styrdes av en bit i statusregistret , PSW. Man skulle lätt kunna växla mellan de två uppsättningarna av register med en enda instruktion. Detta möjliggjorde snabb växling av värden under subrutinsamtal, operativsystemväxlar eller hantering av avbrott. Till skillnad från 1130 var registren bara 8-bitars breda snarare än 16-bitars, och det fanns bara två uppsättningar snarare än de tre i 1130.

En annan av dess miniliknande funktioner var det omfattande stödet för indirekt adressering på de flesta instruktioner. Många instruktioner kräver att data läses från en plats i minnet, i de flesta processorer av eran skulle det vara en enda byte med data som lagras i minnet som refereras till med en 16-bitars plats. I 2650 indikerade den höga biten av den 16-bitarsplatsen inriktning, vilket betyder att data inte fanns på denna plats i minnet, utan den som kodades i de återstående 15 bitarna av adressen. Denna typ av åtkomst gjorde det lättare att komma åt datablock än i system som tillhandahöll indirektion enbart genom speciella instruktioner eller enbart genom indexregister. Man kan gå igenom minnet genom att öka adressvärdet som är lagrat i minnet. Detta resulterade också i att ett stort antal matematiska instruktioner tillämpades på adresser, och för att förbättra prestandan för dessa operationer inkluderade 2650 en andra aritmetisk logikenhet bara för adressberäkningar.

Nackdelen med detta tillvägagångssätt var att den höga biten inte längre var en del av adressen, vilket innebär att adressutrymmet bara var 15 bitar och att maskinen bara kunde komma åt totalt 32 KB minne. Adressutrymmet begränsades ytterligare genom användningen av ytterligare två bitar av adressen för att indikera indexeringsmoden för alla logiska och aritmetiska (dvs icke-gren) instruktioner. Dessa bitar styrde funktioner som om adressen ska efterökas eller försänkas, vilket är extremt användbart för att konstruera slingor. Men med alla dessa bitar redan redovisade, var endast 13 tillgängliga för adresser i dessa instruktioner, vilket betyder att endast 8 KB kunde adresseras direkt. Detta innebar att huvudminnet bröts upp som fyra 8 KB-block. För att komma åt minne utanför de 8 kB där instruktionen fanns, måste databyten som pekades på innehålla en indirekt adress, som pekar på någon annan plats i minnet. Att göra det tvingade fram ytterligare en minnesläscykel, vilket försämrade prestandan.

När 2650 designades 1972 var dessa begränsningar av adressutrymme inte betydande på grund av den lilla storleken och höga kostnaden för det statiska RAM -minnet som vanligtvis används med dessa processorer. Vid den tiden innehöll maskiner vanligtvis 2 eller 4 KB RAM. Men med den ökande användningen av dynamiskt RAM från mitten av 1970-talet blev maskiner med 8 och 16 KB RAM, och i slutändan 64 KB, vanliga och adresseringssystemet på 2650 blev ett betydande hinder.

2650 innehöll också en on-die call stack , snarare än den vanligare lösningen som avsätter en plats i minnet för att hålla stacken. Stackpekaren hölls i tre bitar i PSW . En stack på tärningen är mycket snabbare, eftersom data kan nås direkt utan att vänta på att den ska läsas från externt minne, men den tar också upp plats på tärningen och är alltid begränsad i storlek som ett resultat av praktiska avvägningar. I 2650 var stacken åtta 15-bitars poster djup, vilket i allmänhet är alldeles för litet för att användas för högnivåspråk .

Även om det fanns nio olika adresseringslägen , förhindrade bristen på 16-bitars register och 13–15-bitars adressutrymme utbredd användning. Trots detta fanns ett operativsystem ("2650 DOS") tillgängligt, tillsammans med 8 KB och 12 KB BASIC -tolkar (säljs av Central Data Corporation USA), och många spel i Hunt the Wumpus- stilen. De flesta program skrevs på assemblerspråk .

Används

Signetics sålde 2650-baserade mikroprocessorutvecklingskort , först PC1001 och sedan dess efterföljare, PC1500 "Adaptable Board Computer", med ett pris från 165 A$ till 400 A$. Chipet i sig såldes för cirka 20 A$. Flera hårdvarukonstruktionsprojekt och programmeringsartiklar publicerades i tidningar som Electronics Australia och Elektor och relaterade kit såldes av elektronikbutiker. Dessa faktorer ledde till att den användes av ett antal hobbyister i många länder som Australien, USA, Storbritannien, Nederländerna och Tyskland.

Två typer av videospelskonsoler använde Signetics 2650 eller 2650A. Den första gruppen av konsoler är baserade på Signetics 2636- skärmkontrollern ; 1292 Advanced Programmable Video System och den närbesläktade Interton Video Computer 4000 tillhör denna grupp. De släpptes i Tyskland 1976 respektive 1978. Den andra gruppen av konsoler baserades på Signetics 2637 som en bildskärmskontroller ; Emerson Arcadia 2001 som släpptes 1982 och som använde en Signetics 2650 som körde på 3,58 MHz som CPU tillhör denna grupp tillsammans med många andra programvarukompatibla (Leonardo, Hanimex MPT-03 etc.).

Minst sex myntstyrda videospel släpptes på 1970-talet som använde 2650 CPU: Atari, Inc. Quiz Show , Meadows Games 3D Bowling , Meadows Games Gypsy Juggler , Meadows Games Lazer Command , Cinematronics Embargo och en 1978 clone of Space Invaders av Zaccaria kallas The Invaders (originalet av Taito använder en Intel 8080 CPU).

Den italienska speltillverkaren Zaccaria släppte 28 flipperspel baserade på 2650 CPU. Deras efterträdare företag, MrGame, släppte ytterligare fyra flipperspel med 2650. Zaccaria verkar ha licensierat sin design till Technoplay också, och flera fler flipperspel släpptes med varianter av Zaccarias kretskortsdesigner.

Minst två myntstyrda videospel släpptes på 1980-talet med 2650. Hunchback och Hunchback Olympic.

Processorn användes också i Signetics Instructor 50, som var en liten dator designad för att lära ut användning och programmering av Signetics 2650 CPU.

2650 användes också i en del stora utrustningar som Tektronix 8540, ett utvecklingssystem för mikroprocessorprogramvara som stödde olika in-circuit emulator , spårminne och logiska analysatorkort för realtidsfelsökning av mikroprocessorsystem, som praktiserades på 1980-talet . 2650 gav basoperativsystemets funktioner, dataöverföring och gränssnitt till en värddator eller seriell datorterminal.

Processorn var mest lämpad som en mikrokontroller, på grund av dess omfattande I/O-stöd:

- Enbits i/o-stift på processorn (avkännings-/flaggabitar)

- Signaler för att direkt adressera två 8-bitars I/O-portar (kontroll- och dataportar) med instruktioner för en byte ( port i/o) . Detta kringgick den utarbetade hårdvaran som andra system behövde för minnesmappad I/O

- Signaler för att adressera ytterligare 256 I/O-portar med hjälp av en 8-bitars adress och två byte instruktioner, återigen, vilket begränsar mängden hårdvara (adressavkodning) som krävs. Philips betonade denna användning som en mikrokontroller med ett demonstrationsprogram som visar att 2650 styr ett intelligent hisssystem. På mässor visade de också 2650:an som styrde en miniatyr "sortera och stapla" robot

Industriellt mikrodatorsystem – IMS

Under en kort tid från 1979 sålde Philips en modulär 2650-dator kallad "IMS" – Industrial Microcomputer System, baserat på Eurocard- formatet i ett 19" rack. Den inkluderade CPU , PROM, RAM , ingångs-, utgångs- och teletypmoduler. Systemet var avsett som en mer intelligent programmerbar logikkontroller . För utveckling lade de senare till moduler DEBUG, DISPLAY, INTERRUPT och MODEST ((E)PROM programmerare).

Arkitektur

2650 levererades i en 40-stifts plast- eller keramisk DIL- kapsling. En extern enfasig klocksignal och en enda 5V-källa behövdes.

2650 hade många ovanliga egenskaper jämfört med andra mikroprocessorer på den tiden:

- Det var en helt statisk NMOS 8-bitars mikroprocessor. Den statiska naturen var ovanlig för tiden och innebar att processorn kunde stoppas helt enkelt genom att stoppa klocksignalen. Programmerare använde tacksamt denna funktion för att "enkla steg" genom ett program med en tryckknappsbrytare för att generera klockpulserna.

- Unik var den 8-nivåer 15-bitars breda stacken för subrutinen och avbrottsreturadresserna som var integrerad i processorn. Stackpekaren använde 3 bitar av det övre statusregistret. Detta innebar att subrutiner och avbrott endast kunde kapslas 8 nivåer djupa.

- Processorn hade bara 13 riktiga adresslinjer, ytterligare 2 adresslinjer var anslutna till ett 2-bitars "sidregister", vilket resulterade i ett 32 KB adressutrymme. Sidregistret sattes när en absolut (direkt) greninstruktion, som använde en fullständig 15-bitars adress, exekverades. Alla logiska och aritmetiska instruktioner använde en 13-bitars adress utökad med innehållet i sidregistret, vilket begränsade deras omfattning till en sida på 8 KB. Dessa två övre adressrader användes också (multiplexerade) för att välja lämplig I/O-port under I/O-operationer (kontrollport, dataport eller utökad port).

- Även om 2650 bara hade en avbrottsingång, var detta ett "vektorat" avbrott - den avbrytande enheten behövde för att sätta en noll-relativ förskjutning på databussen, som skulle användas som operand för en ZBSR (nollgren till subrutin-relativ) instruktion att förgrena sig till den specificerade avbrottsrutinen. Med användning av indirekt adressering kunde därför maximalt 30 avbrottsvektorer lagras i de första 64 byten i minnet. (De första tre byten behövdes för att hålla en ovillkorlig gren till rutinen 'återställning'). Detta vektoriserade avbrott påminner också om minidatorn PDP-11 .

Instruktionsuppsättning

Även om 2650 i grunden är en 8-bitars mikroprocessor, är 64 op-koder faktiskt 9-bitar och ytterligare 32 op-koder är 11-bitar (med hjälp av bitar i adressfältet). Av de återstående 128 8-bitars opkoderna är 124 (126 i 2650B) implementerade, vilket ger totalt 444 (446) instruktioner.

Många fler instruktioner finns tillgängliga eftersom beteendet hos standardinstruktionerna kan modifieras genom att ställa in eller radera statusbitar: WC (med eller utan carry) och COM (logisk eller aritmetisk jämförelse). Detta fördubblade antalet rotera, addera, subtrahera och jämföra instruktioner.

Instruktionsuppsättningen är starkt ortogonal : alla logiska och aritmetiska instruktioner kan använda alla nio adresseringslägen:

- Registrera

- omedelbar

- PC-relativ och PC-relativ indirekt

- absolut och absolut indirekt

- absolut indexerad, absolut indexerad med automatisk ökning, och absolut indexerad med automatisk minskning, både direkt och indirekt

Den mest signifikanta biten av alla relativa och absoluta adresser används för att indikera indirektion .

De enda undantagen är när opkoderna för meningslösa operationer används för andra ändamål:

- op-koden för OCH-register noll med register noll används för HALT-instruktionen.

- op-koden för STORE register noll till register noll används för NOP- instruktionen.

Även om instruktionen LADDA register noll med register noll skulle verka meningslös och inte stöddes officiellt, satte den villkorskoden och användes ofta för att fastställa statusen för detta register. [ citat behövs ] . Signetics Assembler genererade kod som om det var instruktionen IORZ,R0 istället.

Indexering

Med alla aritmetiska och logiska instruktioner som använder absolut (direkt) adressering, används bitarna 14 och 13 i adressfältet för att indikera indexeringsläget enligt följande:

- 00 ingen indexering

- 01 indexering med automatisk ökning

- 10 indexering med automatisk minskning

- 11 endast indexering

När indexering specificeras blir registret som definieras i instruktionen indexregistret, och källan/destinationen är implicit Register noll. För indirekt indexering används Post indexing, dvs den indirekta adressen hämtas först från minnet och sedan läggs index till den.

Förgrening

Förmodligen den mest minidatorliknande aspekten av 2650 är det enorma antalet (62) greninstruktioner (hopp); alla dessa instruktioner kan också använda indirekt:

- BIRR och BIRA: Inkrementera register och gren om icke-noll (R0, R1, R2 eller R3) med relativ eller absolut adressering

- BDRR och BDRA: Minska register och gren om icke-noll (R0, R1, R2 eller R3) med relativ eller absolut adressering

- BRNR och BRNA: förgrena sig om registret inte är noll (R0, R1, R2 eller R3) med relativ eller absolut adressering

- BCTR och BCTA: gren på villkor Sant (noll, större än, mindre än eller ovillkorlig) med relativ eller absolut adressering

- BCFR och BCFA: gren på villkor Falskt (noll, större än eller mindre-än) med relativ eller absolut adressering.

- ZBRR: gren i förhållande till adress noll

- BXA: grenindexerad

Liksom Intel 8080 hade 2650 instruktioner för att villkorligt förgrena sig till och återvända från en subrutin:

- BSTR och BSTA: förgrena sig till subrutin på villkor Sant (noll, större än, mindre än eller ovillkorligt) med relativ eller absolut adressering

- BSFR och BSFA: förgrena sig till subrutin på villkor False (noll, större än eller mindre än) med relativ eller absolut adressering

- BSNR och BSNA: förgrena sig till subrutin om registret inte är noll (R0, R1, R2 eller R3) med relativ eller absolut adressering

- RETC: återvända från subrutin på villkor Sant (noll, större än, mindre än eller ovillkorligt)

- RETE: återvänder från avbrott på villkor Sant (noll, större än, mindre än eller ovillkorligt)

- ZBSR: förgrena sig till subrutin i förhållande till adress noll

- BSXA: förgrena sig till subrutin indexerad

Endast greninstruktionerna som använder absolut adressering använde alla 15 bitar i adressfältet som adress. Att använda en sådan greninstruktion var därför det enda sättet att ställa in de två bitarna i sidregistret (kontrollera bitarna 14 och 13 i adressbussen) och ändra den aktuella sidan på 8 KB.

Versioner

- 2650 originalversion med 1,25 MHz maximal klockfrekvens

- 2650A förbättrad version (mindre tillverkningsändringar för att förbättra stabiliteten) 1,25 MHz maximal klockfrekvens

- 2650A-1 som 2650A med 2 MHz maximal klockfrekvens

- 2650B

- 2650B-1 som 2650B med 2 MHz maximal klockfrekvens

2650B hade följande ändringar och förbättringar jämfört med 2650A:

- Två nya signaler – "Bus Enable" på stift 15 och "Cycle Last" på stift 25.

- Programstatusord Övre bitar 3 och 4 är inställbara och testbara användarflaggor (oanvända på 2650A).

- Två nya instruktioner för att spara och återställa det nedre statusregistret för att förenkla avbrottsbehandlingen.

- Enkelbyteregister R0-instruktioner exekveras snabbare (en cykel snarare än två).

Andra källor

1975 såldes Signetics till Philips och 2650 införlivades senare i Philips Semiconductors- linje. De gjorde en version av 2650 som heter MAB2650A. Valvo, ett dotterbolag till Philips, sålde 2650 i Tyskland. Valvo sålde även VA200 single board (Eurocard) 2650-datorn med 4 KB PROM/EPROM, 1 KB RAM och fyra I/O-portar.

Andra tillverkare av licensierade kopior av chipet var Harris och Intersil .

Perifera chips

2650 kom med ett komplett komplement av perifera chips:

- 2621 Video Encoder (PAL)

- 2622 Video Encoder (NTSC)

- 2636 Programmerbart videogränssnitt

- 2637 Universal Video Interface

- 2651 Programmerbart kommunikationsgränssnitt

- 2652 Multi-Protocol Communications Circuit (inkl. Synchronous Data Link Control (SDLC))

- 2653 Polynomgenerator / Checker

- 2655 Programmerbart perifert gränssnitt

- 2656 SMI (Systemminnesgränssnitt)

- 2657 Direkt minnesåtkomst

- 2661 Enhanced Programmable Communication Interface (EPCI)

- 2670 Display Character and Graphics Generator

- 2671 Programmerbart tangentbord och kommunikationskontroll

- 2672 Programmerbar Video Timing Controller

- 2673 Video Attribut Controller

Många av dessa kringutrustningschips designades så att de också kunde användas med andra mikroprocessorer, till exempel föreslår databladet för 2672 att använda det med en Intel 8048 mikrokontroller .

Philips Technical Note 083 beskriver hur man ansluter 2651 PCI till olika andra mikroprocessorer, såsom 8080, 8085, Z80, 8048 och 6800

Ättlingar till 2651/2661 seriella kommunikationskretsar säljs fortfarande som Philips SC26-serien.

2656 Systemminnesgränssnitt

2656 designades speciellt för att utöka och samverka med 2650 och göra en 2-chip dator möjlig. Den innehöll allt som 2650 saknade för att göra en komplett dator:

- 2 KB 8-bitars maskprogrammerat ROM-programminne

- 128 byte 8-bitars RAM-minne

- Klockgenerator med kristall- eller RC-nätverk

- Startåterställning

- Åtta allmänna I/O-stift

I/O-stiften kan användas som en 8-bitars I/O-port eller programmeras för att generera aktiveringssignaler för extra RAM-, ROM- eller I/O-portar. Detta uppnåddes genom att maskprogrammera en programmerbar logisk array i 2656.

För att utveckla och testa designen innan den sattes i produktion sålde Philips PC4000, ett 2656 emulatorkort som använder PROM och FPLA för att emulera ROM och PLA i 2656.

Anteckningar

Citat

Bibliografi

- Rowe, Jamieson (september 1976). "The Signetics 2650" (PDF) . Elektronik Australien .

externa länkar

- 2650 emulatorer

- Datablad

- Signetics 2650 familjens CPU World

- Instruktör 50 Old-computers.com

- Anpassningsbart kortdatorutvecklingssystem komplett med 1 KiB PipBug- monitor och 512 byte RAM

- 2650 på www.cpu-museum.com (arkiverad)

- Electronics Australia 2650-kort på yesterdaystechnology.com

- Signetics 2650: An IBM on a Chip retrospektiv på CPUSHACK Museum (16 oktober 2016)

- Zaccaria The Invaders på Museum of the Game

- En 2650 cross assembler är tillgänglig från https://shop-pdp.net/index.php