Aritmetisk logisk enhet

| Del av en serie om | |||||||

| aritmetiska logiska kretsar | |||||||

|---|---|---|---|---|---|---|---|

| Snabbnavigering | |||||||

|

Komponenter

|

|||||||

|

Kategorier |

|||||||

|

Se även |

|||||||

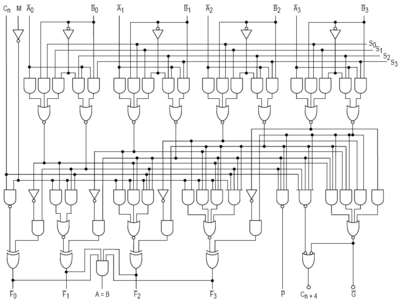

Vid beräkning är en aritmetisk logisk enhet ( ALU ) en kombinationsdigital krets som utför aritmetiska och bitvisa operationer på heltals binära tal . Detta till skillnad från en flyttalsenhet (FPU), som arbetar med flyttal . Det är en grundläggande byggsten i många typer av datorkretsar, inklusive den centrala processorenheten (CPU) för datorer, FPU:er och grafikprocessorer (GPU).

Ingångarna till en ALU är de data som ska opereras på, kallade operander , och en kod som indikerar operationen som ska utföras; ALU:s utsignal är resultatet av den utförda operationen. I många konstruktioner har ALU även statusingångar eller utgångar, eller båda, som förmedlar information om en tidigare operation respektive den aktuella operationen mellan ALU och externa statusregister .

Signaler

En ALU har en mängd olika in- och utgångsnät, som är de elektriska ledare som används för att överföra digitala signaler mellan ALU och externa kretsar. När en ALU är i drift, applicerar externa kretsar signaler till ALU-ingångarna och, som svar, producerar och överför ALU signaler till externa kretsar via dess utgångar.

Data

En grundläggande ALU har tre parallella databussar bestående av två ingångsoperander ( A och B ) och en resultatutgång ( Y ). Varje databuss är en grupp av signaler som förmedlar ett binärt heltal. Typiskt är A-, B- och Y-bussbredderna (antalet signaler som utgör varje buss) identiska och matchar den ursprungliga ordstorleken för den externa kretsen (t.ex. den inkapslande CPU:n eller annan processor).

Opcode

Opkodingången är en parallell buss som överför till ALU en operationsvalskod, som är ett uppräknat värde som specificerar den önskade aritmetiska eller logiska operationen som ska utföras av ALU. Opcodens storlek (dess bussbredd) bestämmer det maximala antalet distinkta operationer som ALU kan utföra; till exempel kan en fyrabitars opkod specificera upp till sexton olika ALU-operationer. I allmänhet är en ALU-opkod inte detsamma som en maskinspråksopkod , även om den i vissa fall kan vara direkt kodad som ett bitfält i en maskinspråksopkod.

Status

Utgångar

Statusutgångarna är olika individuella signaler som förmedlar kompletterande information om resultatet av den aktuella ALU-operationen. Allmänna ALU:er har vanligtvis statussignaler som:

- Carry-out , som förmedlar överföringen som är ett resultat av en additionsoperation, lånet som är ett resultat av en subtraktionsoperation eller spillbiten som är ett resultat av en binär skiftoperation.

- Noll , vilket indikerar att alla bitar av Y är logisk noll.

- Negativ , vilket indikerar att resultatet av en aritmetisk operation är negativt.

- Overflow , vilket indikerar att resultatet av en aritmetisk operation har överskridit det numeriska området för Y.

- Paritet , som anger om ett jämnt eller udda antal bitar i Y är logisk etta.

Efter fullbordandet av varje ALU-operation lagras statusutsignalerna vanligtvis i externa register för att göra dem tillgängliga för framtida ALU-operationer (t.ex. för att implementera aritmetik med flera precisioner) eller för att kontrollera villkorlig förgrening . Samlingen av bitregister som lagrar statusutgångarna behandlas ofta som ett enda, flerbitsregister, vilket hänvisas till som "statusregistret" eller "villkorskodregistret".

Ingångar

Statusingångarna tillåter ytterligare information att göras tillgänglig för ALU när en operation utförs. Typiskt är detta en enda "införingsbit" som är den lagrade utförandet från en tidigare ALU-operation.

Kretsdrift

En ALU är en logisk kombinationskrets, vilket betyder att dess utgångar kommer att ändras asynkront som svar på ingångsändringar. Vid normal drift tillförs stabila signaler till alla ALU-ingångarna och när tillräckligt med tid (känd som " utbredningsfördröjningen ") har passerat för signalerna att fortplantas genom ALU-kretsen, visas resultatet av ALU-operationen vid ALU:n utgångar. De externa kretsarna som är anslutna till ALU:n är ansvarig för att säkerställa stabiliteten hos ALU-ingångssignaler under hela operationen, och för att tillåta tillräckligt med tid för signalerna att fortplanta sig genom ALU:n innan sampling av ALU-resultatet.

I allmänhet styr externa kretsar en ALU genom att tillföra signaler till dess ingångar. Typiskt använder de externa kretsarna sekventiell logik för att styra ALU-driften, som stimuleras av en klocksignal med en tillräckligt låg frekvens för att säkerställa tillräckligt med tid för att ALU-utgångarna ska stabiliseras under värsta tänkbara förhållanden.

Till exempel börjar en CPU en ALU-additionsoperation genom att dirigera operander från deras källor (som vanligtvis är register) till ALU:s operandingångar, medan styrenheten samtidigt applicerar ett värde på ALU:s opkodingång, och konfigurerar den att utföra addition. Samtidigt dirigerar CPU:n också ALU-resultatutmatningen till ett destinationsregister som kommer att ta emot summan. ALU:s insignaler, som hålls stabila till nästa klocka, tillåts fortplanta sig genom ALU:n och till destinationsregistret medan CPU:n väntar på nästa klocka. När nästa klocka anländer lagrar destinationsregistret ALU-resultatet och eftersom ALU-operationen har slutförts kan ALU-ingångarna ställas in för nästa ALU-operation.

Funktioner

Ett antal grundläggande aritmetiska och bitvisa logiska funktioner stöds vanligtvis av ALU. Grundläggande, allmänna ALU:er inkluderar vanligtvis dessa operationer i sina repertoarer:

Aritmetiska operationer

- Addera : A och B summeras och summan visas vid Y och utförande.

- Addera med carry : A, B och carry-in summeras och summan visas vid Y och carry-out.

- Subtrahera : B subtraheras från A (eller vice versa) och skillnaden visas vid Y och utförande. För denna funktion är utförande i praktiken en "låna"-indikator. Denna operation kan också användas för att jämföra storleken på A och B; i sådana fall kan Y-utgången ignoreras av processorn, som endast är intresserad av statusbitarna (särskilt noll och negativ) som är resultatet av operationen.

- Subtrahera med lån : B subtraheras från A (eller vice versa) med låna (inbära) och skillnaden visas vid Y och genomför (låna ut).

- Tvås komplement (negerat) : A (eller B) subtraheras från noll och skillnaden visas vid Y.

- Ökning : A (eller B) ökas med ett och det resulterande värdet visas vid Y.

- Minska : A (eller B) minskas med ett och det resulterande värdet visas vid Y.

- Passera genom : alla bitar av A (eller B) visas omodifierade vid Y. Denna operation används vanligtvis för att bestämma pariteten för operanden eller om den är noll eller negativ, eller för att ladda operanden i ett processorregister.

Bitvis logiska operationer

- OCH : bitvis OCH för A och B visas vid Y.

- ELLER : det bitvisa ELLER för A och B visas vid Y.

- Exklusiv-ELLER : den bitvisa XOR för A och B visas vid Y.

- Ettor komplement : alla bitar av A (eller B) är inverterade och visas vid Y.

Bitskiftsoperationer

| Typ | Vänster | Höger |

|---|---|---|

| Aritmetiskt skift |

|

|

| Logiskt skift |

|

|

| Rotera |

|

|

| Rotera genom att bära |

|

|

ALU-skiftoperationer gör att operanden A (eller B) skiftar åt vänster eller höger (beroende på op-koden) och den skiftade operanden visas vid Y. Enkla ALU:er kan vanligtvis bara skifta operanden med en bitposition, medan mer komplexa ALU:er använder trumskiftare som tillåta dem att flytta operanden med ett godtyckligt antal bitar i en operation. I alla enbitars skiftoperationer visas den bit som skiftats ut ur operanden vid utförande; värdet på biten som skiftas in i operanden beror på typen av skift.

- Aritmetisk skiftning : operanden behandlas som ett tvåkomplement heltal, vilket betyder att den mest signifikanta biten är en "tecken"-bit och bevaras.

- Logisk skiftning : en logisk nolla skiftas till operanden. Detta används för att flytta heltal utan tecken.

- Rotera : operanden behandlas som en cirkulär buffert av bitar så att dess minsta och mest signifikanta bitar är effektivt intill varandra.

- Rotera genom bär : bärbiten och operanden behandlas tillsammans som en cirkulär buffert av bitar.

Ansökningar

Aritmetik med flera precision

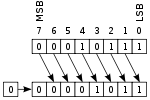

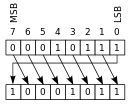

I heltalsaritmetiska beräkningar är aritmetik med flera precision en algoritm som arbetar på heltal som är större än ALU-ordstorleken. För att göra detta behandlar algoritmen varje operand som en ordnad samling av ALU-storleksfragment, arrangerade från mest signifikant (MS) till minst signifikant (LS) eller vice versa. Till exempel, i fallet med en 8-bitars ALU, skulle 24-bitars heltal 0x123456 behandlas som en samling av tre 8-bitars fragment: 0x12 (MS), 0x34 och 0x56 (LS). Eftersom storleken på ett fragment exakt matchar ALU-ordstorleken, kan ALU:n direkt arbeta på denna "bit" av operand.

Algoritmen använder ALU för att direkt operera på särskilda operandfragment och sålunda generera ett motsvarande fragment (ett "partiellt") av multiprecisionsresultatet. Varje partiell, när den genereras, skrivs till en associerad lagringsområde som har utsetts för multipelprecisionsresultatet. Denna process upprepas för alla operandfragment för att generera en komplett samling av partialer, vilket är resultatet av operationen med flera precision.

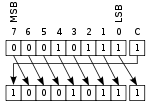

I aritmetiska operationer (t.ex. addition, subtraktion) börjar algoritmen med att anropa en ALU-operation på operandernas LS-fragment, och producerar därigenom både en LS-partial och en utföringsbit. Algoritmen skriver det partiella till det angivna minnet, medan processorns tillståndsmaskin typiskt lagrar utföringsbiten i ett ALU-statusregister. Algoritmen går sedan vidare till nästa fragment av varje operands samling och anropar en ALU-operation på dessa fragment tillsammans med den lagrade överföringsbiten från den föregående ALU-operationen, vilket sålunda producerar en annan (mer signifikant) partiell och en utföringsbit. Som tidigare lagras överföringsbiten i statusregistret och den partiella skrivs till ett avsett minne. Denna process upprepas tills alla operandfragment har bearbetats, vilket resulterar i en komplett samling av partialer i lagring, som omfattar det aritmetiska resultatet med flera precision.

I skiftoperationer med flera precision beror ordningen på operandfragmentbearbetningen på skiftriktningen. I vänsterskiftsoperationer bearbetas fragment LS först eftersom LS-biten för varje partial – som överförs via den lagrade bärbiten – måste erhållas från MS-biten i den tidigare vänsterskiftade, mindre signifikanta operanden. Omvänt behandlas operander MS först i högerskiftningsoperationer eftersom MS-biten för varje partial måste erhållas från LS-biten i den tidigare högerskiftade, mer signifikanta operanden.

I bitvisa logiska operationer (t.ex. logisk AND, logisk ELLER) kan operandfragmenten bearbetas i valfri godtycklig ordning eftersom varje partiell endast beror på motsvarande operandfragment (den lagrade bärbiten från den tidigare ALU-operationen ignoreras).

Komplexa operationer

Även om en ALU kan utformas för att utföra komplexa funktioner, gör den resulterande högre kretskomplexiteten, kostnaden, strömförbrukningen och den större storleken detta opraktiskt i många fall. Följaktligen är ALU ofta begränsade till enkla funktioner som kan exekveras vid mycket höga hastigheter (dvs mycket korta utbredningsfördröjningar), och den externa processorkretsen är ansvarig för att utföra komplexa funktioner genom att orkestrera en sekvens av enklare ALU-operationer.

Till exempel, att beräkna kvadratroten ur ett tal kan implementeras på olika sätt, beroende på ALU-komplexiteten:

- Beräkning i en enda klocka : en mycket komplex ALU som beräknar en kvadratrot i en operation.

- Beräkningspipeline : en grupp av enkla ALU:er som beräknar en kvadratrot i steg, med mellanliggande resultat som passerar genom ALU:er arrangerade som en fabriksproduktionslinje . Denna krets kan acceptera nya operander innan de avslutar de föregående och producerar resultat lika snabbt som den mycket komplexa ALU, även om resultaten fördröjs med summan av utbredningsfördröjningarna för ALU-stegen. För mer information, se artikeln om instruktionspipelining .

- Iterativ beräkning : en enkel ALU som beräknar kvadratroten genom flera steg under ledning av en styrenhet .

Implementeringarna ovan övergår från snabbaste och dyraste till långsammaste och minst kostsamma. Kvadratroten beräknas i alla fall, men processorer med enkla ALU:er kommer att ta längre tid att utföra beräkningen eftersom flera ALU-operationer måste utföras.

Genomförande

En ALU implementeras vanligtvis antingen som en fristående integrerad krets (IC), såsom 74181 , eller som en del av en mer komplex IC. I det senare fallet instansieras en ALU vanligtvis genom att syntetisera den från en beskrivning skriven i VHDL, Verilog eller något annat hårdvarubeskrivningsspråk . Till exempel beskriver följande VHDL-kod en mycket enkel 8-bitars ALU:

0

0

0

0

entitet alu är port ( -- alu-anslutningarna till externa kretsar: A : i signerad ( 7 ner till ); -- operand A B : i signerad ( 7 nedåt ); -- operand B OP : i osignerad ( 2 nedåt ); - - opcode Y : ut signerad ( 7 ner till )); -- operationsresultat slut alu ; arkitekturens beteende hos alu är startfall OP är -- avkoda opkoden och utför operationen: när "000" => Y < = A + B ; -- lägg till när "001" => Y <= A - B ; -- subtrahera när "010" => Y <= A - 1 ; -- minska när "011" => Y <= A + 1 ; -- öka när "100" => Y <= inte A ; -- 1:s komplement när "101" => Y <= A och B ; -- bitvis OCH när "110" => Y <= A eller B ; -- bitvis ELLER när "111" => Y <= A xor B ; -- bitvis XOR när andra => Y <= ( andra => 'X' ); slutfall ; _ slut beteendemässiga ;

Historia

Matematikern John von Neumann föreslog ALU-konceptet 1945 i en rapport om grunden för en ny dator kallad EDVAC .

Kostnaden, storleken och strömförbrukningen för elektroniska kretsar var relativt hög under hela informationsålderns barndom . Följaktligen hade alla seriella datorer och många tidiga datorer, såsom PDP-8 , en enkel ALU som fungerade på en databit i taget, även om de ofta presenterade en bredare ordstorlek för programmerare. En av de tidigaste datorerna som hade flera diskreta enkelbitars ALU-kretsar var 1948 Whirlwind I , som använde sexton sådana "matematikenheter" för att göra det möjligt för den att fungera på 16-bitars ord.

1967 introducerade Fairchild den första ALU implementerad som en integrerad krets, Fairchild 3800, bestående av en åttabitars ALU med ackumulator. Andra ALU:er med integrerade kretsar dök snart upp, inklusive fyrabitars ALU:er som Am2901 och 74181 . Dessa enheter var typiskt " bitslice "-kapabla, vilket betyder att de hade "bär se framåt"-signaler som underlättade användningen av flera sammankopplade ALU-chips för att skapa en ALU med en bredare ordstorlek. Dessa enheter blev snabbt populära och användes i stor utsträckning i bit-slice minidatorer.

Mikroprocessorer började dyka upp i början av 1970-talet. Även om transistorer hade blivit mindre fanns det ofta otillräckligt matrisutrymme för en ALU med full ordbredd och som ett resultat använde vissa tidiga mikroprocessorer en smal ALU som krävde flera cykler per maskinspråksinstruktion. Exempel på detta inkluderar den populära Zilog Z80 , som utförde åttabitars tillägg med en fyrabitars ALU. Med tiden krympte transistorgeometrierna ytterligare, enligt Moores lag , och det blev möjligt att bygga bredare ALU på mikroprocessorer.

Moderna integrerade kretstransistorer (IC) är storleksordningar mindre än de hos de tidiga mikroprocessorerna, vilket gör det möjligt att montera mycket komplexa ALU på IC. Idag har många moderna ALU:er breda ordbredder och arkitektoniska förbättringar såsom tunnskiftare och binära multiplikatorer som tillåter dem att utföra, i en enda klockcykel, operationer som skulle ha krävt flera operationer på tidigare ALU:er.

ALU kan realiseras som mekaniska , elektromekaniska eller elektroniska kretsar [ misslyckad verifiering ] och på senare år har forskning bedrivits på biologiska ALU (t.ex. aktinbaserad ).

Se även

Vidare läsning

- Hwang, Enoch (2006). Digital logik och mikroprocessordesign med VHDL . Thomson. ISBN 0-534-46593-5 .

- Stallings, William (2006). Computer Organization & Architecture: Designing for Performance (7:e upplagan). Pearson Prentice Hall. ISBN 0-13-185644-8 .