Signetics 8X300

| Allmän information | |

|---|---|

| Lanserades | 1976 |

| Designad av | Vetenskapliga mikrosystem (SMS) |

| Vanliga tillverkare |

|

| Prestanda | |

| Max. CPU klockfrekvens | till 8 MHz |

| Databredd | 16 instruktioner, 8 data |

| Adressbredd | 13 instruktion, 1 data |

| Arkitektur och klassificering | |

| Instruktioner | 8 |

| Fysiska specifikationer | |

| Paket(er) |

|

| Historia | |

| Efterträdare | 8X305 |

8X300 är en mikroprocessor som produceras och marknadsförs av Signetics från 1976 som en andra källa för SMS 300 av Scientific Micro Systems, Inc. Även om SMS utvecklade SMS 300, var Signetics den enda tillverkaren av denna produktlinje. 1978 köpte Signetics rättigheterna till SMS 300-serien och döpte om den till 8X300.

Den designades för att vara en snabb mikrokontroller och signalprocessor , och på grund av detta skiljer sig avsevärt från dåtidens konventionella NMOS logiska mikroprocessorer. Den största skillnaden var kanske att den implementerades med bipolär Schottky-transistorteknologi och kunde hämta, avkoda och exekvera en instruktion på endast 250 ns. Data kan matas in från en enhet, modifieras och matas ut till en annan enhet under en instruktionscykel.

1982 släppte Signetics en förbättrad och snabbare version, 8X305. Denna processor blev mycket populär i militära applikationer och kom från Advanced Micro Devices som AM29X305. Så småningom såldes produktionsrättigheterna till Lansdale Semiconductor Inc., som fortfarande erbjöd 8X305 från och med 2017. En klon av 8X300 tillverkades i Sovjetunionen under beteckningen KM1818VM01 ( ryska : КМ1818ВМ01 ).

Arkitektur

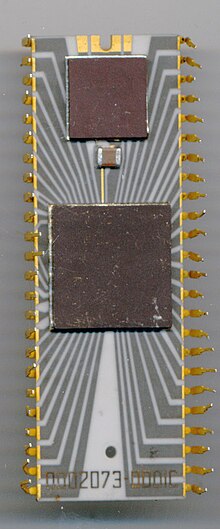

Enheten levererades i ett 50-stifts DIL-keramiskt paket och går från en enda 5V matningsskena. En extern passtransistor krävs för att komplettera en on-chip spänningsregulator, som matar 3V till utvalda delar av chipet. Detta hjälper till att hålla den totala strömförbrukningen till mindre än 450mA.

Klockkraven uppfylls genom att ansluta en 8 MHz kristall direkt till två stift. Alternativt kan urfassignaler från en extern klockgenerator användas.

En andra unik egenskap är en dedikerad 13-bitars adress och 16-bitars databuss för åtkomst till programminne, vilket gör att 8192 16-bitars programord kan adresseras direkt. Detta gör att ROM / PROM-programminnen kan anslutas direkt utan ytterligare hårdvara. En andra kombinerad 8-bitars adress/databuss, Interface Vector (IV) bussen, används för data och I/O. Två styrsignaler, WC (skrivkommando) och SC (välj kommando), bestämmer IV-bussens tillstånd enligt följande:

- SC=1, WC=0: I/O-adress matas ut på IV-bussen

- SC=0, WC=1: I/O-data matas ut på IV-bussen

- SC=0, WC=0: I/O-ingångsdata förväntas på IV-bussen

Ytterligare två signaler, LB (vänster bankval) och RB (höger bankval), fördubblar effektivt IV-bussadressutrymmet och användes oftast för att växla mellan RAM-minne i en bank och I/O-portar i den andra.

En annan ovanlig funktion är att snarare än att utföra maskerings-, rotations-, skift- och sammanfogningsinstruktioner i den aritmetiska logiska enheten (ALU), som är fallet med de flesta mikroprocessorer, har 8X300 separata mask-, rotations-, skift- och sammanfogningsenheter. Data kan därför roteras, maskeras, modifieras, skiftas och slås samman (i den ordningen), allt i en instruktionscykel.

Instruktionsuppsättning

Processorn manipulerar normalt 8-bitars databytes, men maskenheten gör det möjligt att manipulera enstaka eller flera bitar, vilket gör detta till en processor med variabel datalängd. Intern data lagras i 8-bitars läs/skrivregister – R1 till R6, R9 och ett hjälpregister (R0). Hjälpregistret innehåller en av operanderna som används i tvåoperandinstruktioner, såsom ADD eller AND, och ett enbits (skrivskyddat) överflödesregister (R8) lagrar överföringsbiten från ADD-operationer. Två virtuella skrivregister IVL (R7) och IVR (R15) används för att sätta en adress på IV-bussen, och två uppsättningar med åtta virtuella register (R16-R23 och R24-R31) används för att överföra data till eller från IV buss. I det senare fallet väljer de två övre bitarna av registernumret vänster eller höger bank, och de nedre tre bitarna definierar antalet platser som data ska roteras. En 8-bitars IV-bussbuffert behåller en kopia av de senaste data som ska överföras till eller från IV-bussen. Dessa data används i sammanslagningsoperationer.

De tre mest signifikanta bitarna i instruktionen definierar opkoden och delar in instruktionerna i åtta klasser:

- MOVE-instruktionen tillåter att innehållet i valda register kopieras, placeras på IV-bussen, läsas från IV-bussen eller överföras IV-bussen till IV-bussen.

- Klasserna ADD, AND och XOR liknar varandra, förutom att med dessa instruktioner kombineras innehållet i hjälpregistret med källregistret innan MOVE-delen av instruktionen exekveras.

- XEC-instruktionen tillåter att en vald instruktion vid en annan lokal adress och offset exekveras utan att programräknaren ökar.

- NZT-instruktionen tillåter att en villkorlig gren implementeras.

- XMIT-instruktionen tillåter att ett 8-bitars binärt mönster specificerat i instruktionen placeras i ett specificerat register eller på IV-bussen. Det liknar en last-omedelbar instruktion.

- JMP-instruktionen utför en ovillkorlig förgrening till var som helst inom 8192-ordsprogramminnet.

Användningen av de återstående 13 bitarna av instruktionen beror på opkoden:

- MOVE, AND, ADD och XOR-instruktioner: 5 bitar används för att definiera källregistret, 3 bitar används för att definiera valfri rotations- eller maskoperation (R/L-fältet), och de återstående 5 bitarna definierar destinationsregistret.

- XEC och NZT: 5 bitar används för att definiera källregistret, de återstående 8 bitarna definierar adressfältet.

- XEC: innehållet i källregistret läggs först till adressfältet, som sedan används som de nedre 8 bitarna i programadressen.

- NZT: hoppet tas om källregistret inte är noll. Om hoppet tas används adressfältet som de nedre 8 bitarna av programadressen.

- SÄNDNING: 5 bitar används för att definiera destinationsregistret, de återstående 8 bitarna definierar data.

- JMP: alla 13 bitar används som en absolut adress i programminnet.

Skift, rotera, maskera och slå samman

Rotations- och maskenheterna är placerade mellan registerbanken och ALU:n. Därför kan all data i princip roteras och maskeras innan den går in i ALU.

- Rotera enhet: Denna enhet kommer att rotera data åt HÖGER med det antal platser som anges i op-koden.

- Maskenhet: Denna enhet kommer att maskera (inställd på noll) de övre bitarna av datan för att behålla antalet nedre bitar som anges i opkoden.

Shift- och Merge-enheterna är placerade mellan ALU och IV-bussen, och all data som skickas till IV-bussen kan därför skiftas och slås samman innan den matas ut.

- Shift Unit: Denna enhet kommer att flytta data till VÄNSTER det antal platser som anges i op-koden.

- Merge Unit: Denna enhet kommer att slå samman (ersätta) antalet bitar som specificeras av opcoden i IV-bussbufferten med data innan innehållet i bufferten placeras på IV-bussen.

Obs: ett antal bitar som ska sammanfogas kommer att resultera i att alla 8 bitar ersätts.

Följande kombinationer är möjliga, beroende på källa och destination:

- FLYTTA, LÄGG TILL, OCH och XOR instruktioner:

- registrera för att registrera (inklusive IVL- och IVR-register): Rotera

- registrera till IV-buss (datautgång): skift och sammanfoga

- IV-bus-ingång för registrering: rotera och maskera

- IV-bussingång till IV-bussutgång: rotera, maskera, skifta och slå samman

- IV-bus-ingång till IVL- eller IVR-register (IV-bus-adressutgång): rotera och maskera

- XEC och NZT:

- IV-bus-ingång: rotera och maskera

- XMIT

- IV-buss datautgång: skift och sammanfoga

I/O

Att överföra data till och från 8X300 är en process i två steg:

- Steg 1: Genom att använda en av MOVE, ADD, AND, XOR eller XMT instruktionerna och specificera ett av de virtuella registren IVL (vänster bank) eller IVR (höger bank) som destination, matas en adress ut på IV-bussen, tillsammans med Välj kommando- och bankvalsignaler.

Eftersom I/O-adressen matas ut separat måste I/O-portarna hålla (låsa) valet. Detta kan göras med separata adressavkodare och lås, eller med en I/O-port med integrerad adressavkodning och låsning, som t.ex. 8X32. På grund av låsningen förblir I/O-portar, när de väl har adresserats, aktiva tills en annan adress matas ut och kan nås flera gånger utan att behöva adressera dem igen. Två I/O-portar (eller RAM-adresser) kan vara aktiva samtidigt, med hjälp av Bank Select-signalerna för att snabbt växla mellan dem utan ytterligare adressering.

- Steg 2: Data överförs till eller från 8X300 genom att använda en av MOVE, ADD, AND eller XOR instruktionerna och specificera ett av registren R16-R31 som källa och/eller destination. Det valda registret definierar vilken bankvalssignal som följer med överföringen.

Ansökningar

I en omfattande applikationsanteckning visade Signetics hur man använder 8X300 som en diskettkontroller . En reviderad ansökningsnotis visade användningen av 8X300 tillsammans med 8X330. Andra applikationsanmärkningar beskrivs:

- En teletypmultiplexor _

- En datakoncentrator

- En fjärrkontroll för terminaler

- En dator I/O-bussemulator

- Gränssnitt RAM-minne

Ett demonstrationssystem (som finns i en portfölj) och ansökningsnotis visade att 8X300 användes i en trafikljuskontroller.

Olivetti använde 8X300 och senare 8X305 som styrenhet för ST506-hårddisken i persondatorserien M20 .

Convergent Technologies använde 8X300, 8X320 och 8X330 i sin AWS-hårddiskkontroller 1981.

Western Digital använde 8X300 i sin WD1000 ST506 hårddiskkontroller och 8X305 i sin WD1001 ECC hårddiskkontroller.

Stöd enheter

- 8X01: Cyklisk redundanskontroll

- 8X31 / 8T31: 8-bitars låst dubbelriktad I/O-port

- 8X32 / 8X36 / 8X42: 8-bitars låst adresserbar dubbelriktad I/O-port

- 8T39: Adresserbar bussexpander

- 8X41: Asynkron dubbelriktad bussförlängare och repeater (SABRE)

- 8T58: Transparent bussexpander

- 8X320: Bussgränssnittsregisteruppsättning

- 8X330: Diskettformaterare/kontroller

- 8X350: 2048-bitars bipolärt RAM (256*8) 35 ns åtkomsttid

- SMS360 / 8X360: Gränssnittsvektorbyte