WD16

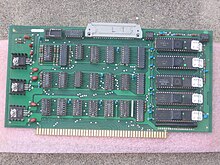

WD16-mikroprocessor i fem 40-stiftspaket installerade på ett Alpha Microsystems AM-100 CPU-kort som ansluts till en S-100-buss .

| |

| Allmän information | |

|---|---|

| Lanserades | 1976 |

| Vanliga tillverkare | |

| Prestanda | |

| Max. CPU klockfrekvens | till 3,3 MHz |

| Databredd | 16 |

| Adressbredd | 16 |

| Arkitektur och klassificering | |

| Instruktionsuppsättning | PDP-11 gillar |

| Instruktioner | 119 |

| Fysiska specifikationer | |

| Paket(er) |

|

| Historia | |

| Efterträdare | ingen |

WD16 är en 16-bitars mikroprocessor som introducerades av Western Digital i oktober 1976. Den är baserad på MCP-1600 -kretsuppsättningen, som utgjorde grunden för DEC LSI-11 low-end minidator och Pascal MicroEngine- processorn designad speciellt för att köra UCSD p-System effektivt. Var och en använde olika mikrokoder. WD16 implementerar en utökning av PDP-11-instruktionsuppsättningsarkitekturen men är inte maskinkodkompatibel med PDP-11. Instruktionsuppsättningen och mikrokodningen skapades av Dick Wilcox och Rich Notari. WD16 är ett exempel på ortogonal CISC-arkitektur . De flesta tvåoperand-instruktioner kan driva minne-till-minne med valfritt adresseringsläge och vissa instruktioner kan resultera i upp till tio minnesåtkomster.

WD16 är implementerad i fem 40-stifts DIP -paket. Maximal klockhastighet är 3,3 MHz. Dess gränssnitt till minnet sker via en 16-bitars multiplexerad data-/adressbuss.

WD16 är mest känd för sin användning i Alpha Microsystems AM-100 och AM-100/T processorkort. En prototyp demonstrerades 1977. Från och med 1981 fanns det minst 5 000 Alpha Micro-datorer baserade på WD16. Så sent som 1982 karakteriserades WD16-baserade Alpha Micros fortfarande som "supermicros". WD16 ersattes av Motorola 68000 i juni 1982.

Minne

Dataformat

Den minsta enheten av adresserbart och skrivbart minne är 8-bitars byte . Byte kan också hållas i den nedre halvan av registren R0 till R5.

16-bitars ord lagras little-endian med minst signifikanta bytes vid den lägre adressen. Ord är alltid anpassade till jämna minnesadresser. Ord kan hållas i registren R0 till R7.

32-bitars dubbla ord kan endast lagras i registerpar med det lägre ordet lagrat i det lägre numrerade registret. 32-bitars värden används av MUL, DIV och vissa rotations- och aritmetiska skiftinstruktioner.

Flyttalsvärden är 48 bitar långa och kan endast lagras i minnet. Detta format är halvvägs mellan enkel- och dubbelprecisions flyttalsformat. De lagras i ett ovanligt middle-endian -format som ibland kallas "PDP-endian". Flyttalsvärden är alltid justerade till jämna adresser. Det första ordet innehåller mantissans tecken, exponent och höga byte. Den nästa högre adressen innehåller de två mittersta byten av mantissan, och den nästa högre adressen innehåller de två lägsta byten av mantissan. Det fullständiga formatet är som följer:

1. Ett 1-bitars tecken för hela talet som är noll för positivt.

2. En 8-bitars bas-två-exponent i notation över 128 med ett intervall på +127, -128. Det enda lagliga numret med exponenten -128 är sann noll (alla nollor).

3. En 40 bitars mantissa med MSB underförstådd.

| 15 | 14 | 7 | 6 | 0 | ||||||||||||

| Addr+0 | S | Exponent | Mantissa (hög) | |||||||||||||

| 15 | 8 | 7 | 0 | |||||||||||||

| Addr+2 | Mantissa | (mitten) | ||||||||||||||

| 15 | 8 | 7 | 0 | |||||||||||||

| Addr+4 | Mantissa | (låg) | ||||||||||||||

Minneshantering

WD16:s 16-bitars adresser kan direkt komma åt 64 KB minne. WD16 erbjuder ingen inneboende minneshantering eller skydd. I AM-100-applikationen mappas de senaste 256 minnesplatserna till portutrymme . Eftersom de flesta AM-100-datorer användes som fleranvändardatorer, skulle minnet vanligtvis utökas till över 64K med bankväxling . Även om AM-100 kan konfigureras för upp till 22 användare och 512 kilobyte RAM, kan en typisk minneskonfiguration för en 9-användare AM-100 vara i intervallet 352 kilobyte. 1981 erbjöds en valfri AM-700 minneshanteringsenhet för AM-100/T som tillät minnessegmentering i steg om 256 byte.

CPU-register

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

CPU:n innehåller åtta allmänna 16-bitars register , R0 till R7. Registren kan användas för alla ändamål med dessa undantag: Register R7 är programräknaren ( PC) . Även om vilket register som helst kan användas som stackpekare, är R6 stackpekaren (SP) som används för hårdvaruavbrott och fällor. R0 är antalet för blocköverföringsinstruktionerna.

Adresseringslägen

De flesta instruktioner allokerar sex bitar för att specificera varje operand. Tre bitar väljer en av åtta adresseringsmoder och tre bitar väljer ett allmänt register. Kodningen av sexbitars operandadresseringsmod är som följer:

| 5 | 3 | 2 | 0 | ||

| Läge | Registrera | ||||

I följande avsnitt innehåller varje objekt ett exempel på hur operanden skulle skrivas på assemblerspråk. Rn betyder ett av de åtta registren, skrivna R0 till R7.

Allmänna registeradresseringslägen

Följande åtta lägen kan tillämpas på vilket allmänt register som helst. Deras effekter när de tillämpas på R6 (stackpekaren, SP) och R7 (programräknaren, PC) anges separat i följande avsnitt.

| Koda | namn | Exempel | Beskrivning |

|---|---|---|---|

| 0n | Registrera | Rn | Operaanden är i Rn |

| 1n | Registrering uppskjuten | (Rn) | Rn innehåller adressen till operanden |

| 2n | Automatisk ökning | (Rn)+ | Rn innehåller adressen till operanden, öka sedan Rn |

| 3n | Autoinkrement uppskjuten | @(Rn)+ | Rn innehåller adressen till operandens adress, öka sedan Rn med 2 |

| 4n | Autodecrement | −(Rn) | Minska Rn, använd sedan resultatet som adress för operanden |

| 5n | Autodecrement uppskjuten | @−(Rn) | Minska Rn med 2, använd sedan resultatet som adressen till operandens adress |

| 6n | Index | X(Rn) | Rn+X är adressen till operanden |

| 7n | Index uppskjuten | @X(Rn) | Rn+X är adressen till operandens adress |

I index- och indexuppskjutna lägen är X ett 16-bitarsvärde taget från ett andra ord i instruktionen. I dubbeloperandinstruktioner kan båda operanderna använda dessa lägen. Sådana instruktioner är tre ord långa.

Autoinkrement- och autodekrementeringsoperationer på ett register är med 1 i byte-instruktioner, med 2 i ordinstruktioner, och med 2 närhelst en uppskjuten mod används, eftersom kvantiteten som registret adresserar är en (ord)pekare.

Programmera räknaradresseringslägen

När R7 (programräknaren) specificeras ger fyra av adresseringslägena naturligtvis användbara effekter:

| Koda | namn | Exempel | Beskrivning |

|---|---|---|---|

| 27 | Omedelbar | #n | Operanden är nästa ord i instruktionen |

| 37 | Absolut | @#a | Adressen till operanden är nästa ord i instruktionen |

| 67 | Relativ | a | Adressen till operanden är nästa ord i instruktionen som läggs till datorn |

| 77 | Anhörig uppskjuten | @a | Adressen till operandens adress är nästa ord i instruktionen som läggs till PC |

Det finns bara två vanliga användningsområden för absolut läge, vars syntax kombinerar omedelbart och uppskjutet läge. Den första är att komma åt de reserverade processorplatserna på 0000-003F. Den andra är att specificera in-/utgångsregister i portutrymmet, eftersom registren för varje enhet har specifika minnesadresser. Relativt läge har en enklare syntax och är mer typiskt för att referera till programvariabler och hoppdestinationer. Ett program som använder relativt läge (och relativt uppskjutet läge) enbart för interna referenser är positionsoberoende ; den innehåller inga antaganden om sin egen plats, så den kan laddas till en godtycklig minnesplats, eller till och med flyttas, utan att dess adresser behöver justeras för att återspegla sin plats. Vid beräkning av sådana adresser i förhållande till den aktuella platsen, utför processorn omlokalisering i farten.

Omedelbara och absoluta lägen är endast autoinkrement respektive autoincrement uppskjutet läge, applicerade på PC. När hjälpordet finns i instruktionen, inkrementeras PC:n för nästa instruktion automatiskt förbi hjälpordet. Eftersom PC alltid pekar på ord, är den automatiska ökningen alltid med ett steg på 2.

Stack adresseringslägen

R6, även skrivet SP, används som en hårdvarustack för fällor och avbrott. En konvention som upprätthålls av uppsättningen adresseringslägen som WD16 tillhandahåller är att en stack växer nedåt - mot lägre adresser - när objekt skjuts på den. När ett läge tillämpas på SP, eller på något register som programmeraren väljer att använda som en mjukvarustack, har adresseringslägena följande effekter:

| Koda | namn | Exempel | Beskrivning |

|---|---|---|---|

| 16 | Uppskjuten | (SP) | Operanden finns på toppen av stapeln |

| 26 | Automatisk ökning | (SP)+ | Operanden är på toppen av stapeln, skjut sedan av den |

| 36 | Autoinkrement uppskjuten | @(SP)+ | En pekare till operanden är överst i stacken; dra av pekaren |

| 46 | Autodecrement | −(SP) | Skjut ett värde på stapeln |

| 66 | Indexerad | X(SP) | Operaanden är placerad X avstånd från toppen av stapeln |

| 76 | Indexerad uppskjuten | @X(SP) | Pekaren till operanden är placerad X avstånd från toppen av stacken |

Även om mjukvarustackar kan innehålla bytes, pekar SP alltid på en hög med ord. Autoinkrement och autodecrement operationer på SP är alltid med ett steg på 2.

Instruktionsuppsättning

De flesta av WD16-instruktionerna fungerar på byte och ord. Byte specificeras av ett registernummer – som identifierar registrets lågordningsbyte – eller av en minnesplats. Ord specificeras av ett registernummer eller av minnesplatsen för den låga ordningens byte, som måste vara ett jämnt tal. I listorna i följande avsnitt är bokstaven B fogad till instruktionssymbolen för att specificera en byteoperation, till exempel blir MOV MOVB. Alla opkoder och adresser är uttryckta i hexadecimal .

Dubbeloperand instruktioner

bitarna av hög ordning anger operationen som ska utföras. Två grupper om sex bitar specificerar källoperandadresseringsmoden och destinationsoperandadresseringsmoden, såsom definierats ovan.

| 15 | 12 | 11 | 9 | 8 | 6 | 5 | 3 | 2 | 0 | ||||||

| Opcode | Src | Registrera | Dest | Registrera | |||||||||||

| Opcode | Mnemonic | Drift |

|---|---|---|

| 1000 | LÄGG TILL | Lägg till: Dest ← Dest + Src

|

| 2000 | SUB | Subtrahera: Dest ← Dest - Src

|

| 3000 | OCH | Och: Dest ← Dest ∧ Src

|

| 4000 | BIC | Lite tydligt: Dest ← Dest ∧ (-1 - Src)

|

| 5 000 | BIS | Bit Set: Dest ← Dest ∨ Src

|

| 6000 | XOR | Exklusiv eller: Dest ← Dest ⊻ Src

|

| 9000 | CMP | Jämför: Set-flags(Src − Dest)

|

| A000 | BIT | Bittest: Set-flags(Dest ∧ Src)

|

| B000 | MOV | Flytta: Dest ← Src

|

| C000 | CMPB | Jämför byte: Set-flags(Src − Dest)

|

| D000 | MOVB | Flytta byte: Dest ← Src (Register destination sign-extends in bits 8-15) |

| E000 | BISB | Bituppsättning byte: Dest ← Dest ∨ Src

|

Vissa tvåoperandinstruktioner använder ett adresseringsläge för en operand och ett register för den andra operanden:

| 15 | 9 | 8 | 6 | 5 | 3 | 2 | 0 | ||||||||

| Opcode | Reg | Src/Dest | Registrera | ||||||||||||

De sju bitarna av hög ordning specificerar operationen som ska utföras, sex bitar specificerar operandadresseringsmoden och tre bitar specificerar ett register eller registerpar. Där ett registerpar används (skrivet nedan som "Reg+1:Reg") innehåller Reg den låga delen av operanden. Det nästa högre numrerade registret innehåller den höga ordningens del av operanden (eller resten).

| Opcode | Mnemonic | Drift |

|---|---|---|

| 7200 | LEA | Ladda effektiv adress: Reg ← ea(Dest)

|

| 7200 | JMP | Hoppa: PC ← ea(Dest) (Detta är samma som LEA PC,Dest och delar samma opkod.) |

| 7400 | ASKA | Aritmetiskt skift: om Src < 0 så Reg ← Skift-höger(Reg, -Src) annars Reg ← Skift-vänster(Reg, Src)

|

| 7800 | XCH | Utbyte: Reg ↔ Src

|

| 7A00 | ASHC | Aritmetiskt skift kombinerat (32 bitar): om Src < 0 då (Reg+1:Reg) ← Skift-höger((Reg+1:Reg), -Src) annat (Reg+1:Reg) ← Skift-vänster(( Reg+1:Reg), Src)

|

| 7C00 | MUL | Multiplicera: (Reg+1:Reg) ← Reg × Src

|

| 7E00 | DIV | Divide: Beräkna (Reg+1:Reg) ÷ Src; Reg ← kvot; Reg+1 ← resten

|

Enkeloperandinstruktioner

De tio bitarna av hög ordning anger operationen som ska utföras, varvid bit 15 i allmänhet väljer byte kontra ordadressering. En enda grupp om sex bitar specificerar operanden enligt definitionen ovan.

| 15 | 6 | 5 | 3 | 2 | 0 | ||||||||||

| Opcode | Src/Dest | Registrera | |||||||||||||

| Opcode | Mnemonic | Drift |

|---|---|---|

| 0BC0 | SVABB | Byt byte av ord: Dest ← (Dest × 256) ∨ (Dest ÷ 256)

|

| 8BC0 | SWAD | Byt siffror i byte: Dest ← (Dest × 16) ∨ (Dest ÷ 16)

|

| 0840 | CLR | Rensa: Dest ← 0

|

| 8840 | CLRB | |

| 0C00 | COM | Komplement: Dest ← (-1 - Dest)

|

| 8C00 | HÅRKAM | |

| 0C80 | INC | Öka: Dest ← Dest + 1

|

| 8C80 | INCB | |

| 0CC0 | DEC | Minska: Dest ← Dest − 1

|

| 8CC0 | DECB | |

| 0C40 | NEG | Negate: Dest ← -Dest

|

| 8C40 | NEGB | |

| 0B00 | UPPSÄTTNING | Set: Dest ← -1

|

| 8B00 | SETB | |

| 0A80 | TST | Test: Set-flags(Src)

|

| 8A80 | TSTB | |

| 0A00 | ROR | Rotera åt höger: Dest:Cflag ← Rotate-right(Dest:Cflag, 1)

|

| 8A00 | RORB | |

| 0A40 | ROL | Rotera vänster: Cflag:Dest ← Rotate-left(Cflag:Dest, 1)

|

| 8A40 | ROLB | |

| 0B80 | ASR | Aritmetiskt skift höger: Dest ← Dest ÷ 2, tecken bevarat

|

| 8B80 | ASRB | |

| 0AC0 | ASL | Aritmetisk förskjutning vänster: Dest ← Dest × 2

|

| 8AC0 | ASLB | |

| 8D80 | ADC | Lägg till carry: Dest ← Dest + Cflag

|

| 8DC0 | SBC | Subtrahera carry: Dest ← Dest - Cflag

|

| 0D00 | IW2 | Öka ord med 2: Dest ← Dest + 2

|

| 0DC0 | TJMP | Tabellhopp: PC ← PC + (Dest), PC ← PC + @PC

|

| 0D80 | TCALL | Tabellanrop: -(SP) ← PC, PC ← PC + (Dest), PC ← PC + @PC

|

| 0D40 | SXT | Teckenförlängning: om N flagga = 1 så Dest ← -1 annars Dest ← 0

|

| 8D00 | LSTS | Belastningsprocessorstatus: PSW ← Dest

|

| 8D40 | SSTS | Spara processorstatus: Dest ← PSW

|

Enkeloperand korta omedelbara instruktioner

De sju höga bitarna och bitarna 5 och 4 specificerar operationen som ska utföras. En enda grupp om tre bitar specificerar registret. Ett fyrabitars räknefält innehåller en liten omedelbar räkning eller en räkning. I alla fall läggs ett till i detta fält, vilket gör intervallet 1 till 16.

| 15 | 9 | 8 | 6 | 5 | 4 | 3 | 0 | ||||||||

| Opcode | Reg | Op | Räkna | ||||||||||||

| Opcode | Mnemonic | Drift |

|---|---|---|

| 0800 | ADDI | Lägg till omedelbart: Reg ← Reg + Count + 1

|

| 0810 | SUBI | Subtrahera omedelbart: Reg ← Reg - Räkna - 1

|

| 0820 | BICI | Lite tydligt omedelbart: Reg ← Reg ∧ (-1 - (Count+1))

|

| 0830 | MOVI | Flytta omedelbart: Reg ← Räkna + 1

|

| 8800 | SSRR | Högerrotera multipel: Reg:C-flagga ← Rotera-höger(Reg:C-flagga, Count+1)

|

| 8810 | SSLR | Vänsterrotera multipel: C-flagga:Reg ← Rotera-vänster(C-flagga:Reg, Count+1)

|

| 8820 | SSRA | Höger aritmetisk skiftmultipel: Reg:C-flagga ← Aritmetisk skift-höger(Reg, Count+1)

|

| 8830 | SSLA | Vänster aritmetisk skiftmultipel: C-flagga:Reg ← Aritmetisk-skift-vänster(Reg, Count+1)

|

| 8E00 | SDRR | Dubbel högerrotera multipel (33 bitar): Reg+1:Reg:C-flagga ← Rotera-höger(Reg+1:Reg:C-flagga, Count+1)

|

| 8E10 | SDLR | Dubbel vänsterrotera multipel (33 bitar): C-flagga:Reg+1:Reg ← Rotera-vänster(C-flagga:Reg+1:Reg, Count+1)

|

| 8E20 | SDRA | Dubbel höger aritmetisk skiftmultipel (32 bitar): Reg:Reg+1:C-flagga ← Aritmetisk-shift-höger(Reg:Reg+1, Count+1)

|

| 8E30 | SDLA | Dubbel vänster aritmetisk skiftmultipel (32 bitar): C-flagga:Reg:Reg+1 ← Aritmetisk skift-vänster(Reg:Reg+1, Count+1)

|

Flyttalsinstruktioner

De åtta bitarna av hög ordning anger operationen som ska utföras. Två grupper om fyra bitar anger käll- och destinationsadresseringsläge och register. Om fält I = 0, innehåller det angivna registret adressen för operanden, motsvarande adresseringsmod (Rn). Om fält I = 1, innehåller det designerade registret adressen till operandens adress, motsvarande adresseringsmod @0(Rn).

| 15 | 8 | 7 | 6 | 4 | 3 | 2 | 0 | ||||||||

| Opcode | jag | SReg | jag | DReg | |||||||||||

| Opcode | Mnemonic | Drift |

|---|---|---|

| F000 | FADD | Flytande tillägg: Dest ← Dest + Src

|

| F100 | FSUB | Flytande subtrahera: Dest ← Dest - Src

|

| F200 | FMUL | Flytande multiplicera: Dest ← Dest × Src

|

| F300 | FDIV | Floating Divide: Dest ← Dest ÷ Src

|

| F400 | FCMP | Flytande Jämför: Dest - Src

|

Blockera överföringsinstruktioner

De tio bitarna av hög ordning anger operationen som ska utföras. Två grupper om tre bitar anger käll- och destinationsregistren. I alla fall innehåller källregistret adressen för det första ordet eller byten i minnet som ska flyttas, och destinationsregistret innehåller adressen för det första ordet eller byten i minnet för att ta emot data som flyttas. Antalet ord eller bytes som flyttas finns i R0 som ett heltal utan tecken. Antalet sträcker sig från 1–65536. Dessa instruktioner är helt avbrytbara.

| 15 | 6 | 5 | 3 | 2 | 0 | ||||||||||

| Opcode | SReg | DReg | |||||||||||||

| Opcode | Mnemonic | Drift |

|---|---|---|

| 0E00 | MBWU | Flytta ordblock uppåt: (DReg) ← (SReg), SReg ← SReg + 2, DReg ← DReg + 2, R0 ← R0 - 1, tills R0 = 0

|

| 0E40 | MBWD | Flytta ordblock nedåt: (DReg) ← (SReg), SReg ← SReg - 2, DReg ← DReg - 2, R0 ← R0 - 1, tills R0 = 0

|

| 0E80 | MBBU | Flytta block med byte upp: (DReg) ← (SReg), SReg ← SReg + 1, DReg ← DReg + 1, R0 ← R0 - 1, tills R0 = 0

|

| 0EC0 | MBBD | Flytta block med byte nedåt: (DReg) ← (SReg), SReg ← SReg - 1, DReg ← DReg - 1, R0 ← R0 - 1, tills R0 = 0

|

| 0F00 | MBWA | Flytta ordblock till adressen: (DReg) ← (SReg), SReg ← SReg + 2, R0 ← R0 - 1, tills R0 = 0

|

| 0F40 | MBBA | Flytta block med byte till adressen: (DReg) ← (SReg), SReg ← SReg + 1, R0 ← R0 - 1, tills R0 = 0

|

| 0F80 | MABW | Flytta adress till ordblock: (DReg) ← (SReg), DReg ← DReg + 2, R0 ← R0 - 1, tills R0 = 0

|

| 0FC0 | MABB | Flytta adress till block av byte: (DReg) ← (SReg), DReg ← DReg + 1, R0 ← R0 - 1, tills R0 = 0

|

Branschanvisningar

Instruktionens byte av hög ordning anger operationen. Den låga ordningens byte är en teckenordsförskjutning relativt den aktuella platsen för programräknaren. Detta möjliggör framåt- och bakåtgrenar i kod. Maximalt grenintervall är +128, -127 ord från grenoperationskoden.

I de flesta greninstruktioner baseras om grenen tas på tillståndskodernas tillstånd. En greninstruktion föregås vanligtvis av en tvåoperand CMP (jämför) eller BIT (bittest) eller en enoperand TST (test) instruktion. Aritmetiska och logiska instruktioner ställer också in villkorskoderna. I motsats till Intel- processorer i x86-arkitekturen ställer MOV-instruktioner in dem också, så en greninstruktion kan användas för att förgrena sig beroende på om det flyttade värdet var noll eller negativt.

| 15 | 8 | 7 | 0 | ||||||||||||

| Opcode | Offset | ||||||||||||||

| Opcode | Mnemonic | Skick eller funktion |

|---|---|---|

| 0100 | BR | Filial alltid PC ← PC + (2 × Sign-extend(Offset))

|

| 0200 | BNE | Gren om inte lika med Z = 0

|

| 0300 | BEQ | Gren om lika med Z = 1

|

| 0400 | BGE | Gren om större än eller lika med (N ⊻ V) = 0

|

| 0500 | BLT | Gren om mindre än (N ⊻ V) = 1

|

| 0600 | BGT | Gren om större än (Z ∨ (N ⊻ V)) = 0

|

| 0700 | BLE | Gren om mindre än eller lika med (Z ∨ (N ⊻ V)) = 1

|

| 8000 | BPL | Gren om plus N = 0

|

| 8100 | BMI | Gren om minus N = 1

|

| 8200 | BHI | Gren om högre (C ∨ Z) = 0

|

| 8300 | BLOS | Gren om lägre eller samma (C ∨ Z) = 1

|

| 8400 | BVC | Förgrening om bräddavloppsfri V = 0

|

| 8500 | BVS | Förgrening om bräddsats V = 1

|

| 8600 | BCC eller BHIS | Gren om bär fri, eller gren om högre eller samma C = 0

|

| 8700 | BCS eller BLO | Gren om bärset, eller gren om lägre C = 1

|

Det begränsade omfånget för greninstruktionerna innebar att när koden växer kan måladresserna för vissa grenar bli oåtkomliga. Programmeraren skulle ändra Bcc med ett ord till JMP-instruktionen med två ord. Eftersom JMP inte har några villkorliga former, skulle programmeraren ändra Bcc till dess motsatta betydelse för att förgrena sig runt JMP.

SOB (Subtract One and Branch) är en annan villkorlig greninstruktion. Det specificerade registret minskas med 1, och om resultatet inte är noll, tas en omvänd gren baserat på 6-bitars ordförskjutning.

| 15 | 9 | 8 | 6 | 5 | 0 | ||||||||||

| Opcode | Reg | Offset | |||||||||||||

| Opcode | Mnemonic | Drift |

|---|---|---|

| 7600 | SNYFTA |

Subtrahera ett och gren: Reg ← Reg - 1; om Reg ≠ 0 så PC ← PC - (2 × Offset)

|

Subrutin instruktioner

JSR-instruktionen kan spara vilket register som helst på stacken. Program som inte behöver denna funktion anger PC som register (JSR PC, adress) och subrutinen returnerar med RTN PC. Om en rutin anropades med till exempel "JSR R4, adress", så skulle det gamla värdet på R4 sparas överst i stacken och returadressen (strax efter JSR) skulle vara i R4. Detta låter rutinen få tillgång till värden kodade in-line genom att specificera (R4)+ eller till in-line-pekare genom att specificera @(R4)+. Autoinkrementeringen går förbi dessa data, till den punkt där uppringarens kod återupptas. En sådan rutin skulle behöva specificera RTN R4 för att återvända till sin uppringare.

Formuläret JSR PC,@(SP)+ kan användas för att implementera koroutiner . Initialt placeras ingångsadressen för koroutinen på stacken och från den punkten används instruktionen JSR PC,@(SP)+ för både anrops- och retursatserna. Resultatet av denna JSR-instruktion är att utbyta innehållet i PC:n och det översta elementet i stacken, och på så sätt tillåta de två rutinerna att byta kontroll och återuppta drift där var och en avslutades av det föregående bytet.

| 15 | 9 | 8 | 6 | 5 | 3 | 2 | 0 | ||||||||

| Opcode | Reg | Src | Registrera | ||||||||||||

| Opcode | Mnemonic | Drift |

|---|---|---|

| 7000 | JSR | Hoppa till subrutin: -(SP) ← Reg; Reg ← PC; PC ← Src

|

| 15 | 3 | 2 | 0 | ||||||||||||

| Opcode | Reg | ||||||||||||||

| Opcode | Mnemonic | Drift |

|---|---|---|

| 0018 | RTN | Retur från subrutin: PC ← Reg; Reg ← (SP)+

|

| 0028 | PRTN | Pop stack och retur: SP ← SP + (2 × @SP), PC ← Reg; Reg ← (SP)+

|

Instruktioner för enstaka register

Dessa instruktioner har en 13 bitars opkod och ett trebitars registerargument.

| 15 | 3 | 2 | 0 | ||||||||||||

| Opcode | Reg | ||||||||||||||

| Opcode | Mnemonic | Drift |

|---|---|---|

| 0010 | IAK | Interrupt acknowledge: Interrupt acknowledge state code, Reg ← Bus read

|

| 0020 | MSKO | Mask ut: (002E) ← Reg, Mask ut tillståndskod

|

Underförstådda parameterinstruktioner

| 15 | 0 | ||||||||||||||

| Opcode | |||||||||||||||

| Opcode | Mnemonic | Drift |

|---|---|---|

| 0000 | NEJ | Ingen operation: Gör ingenting

|

| 0001 | ÅTERSTÄLLA | Återställning: Sänd återställningspuls till I/O-enheter

|

| 0002 | IEN | Avbrottsaktivering: I2 ← 1

|

| 0003 | IDS | Avbryt avbrott: I2 ← 0

|

| 0004 | STANNA | Stoppa: Kör det valda stoppalternativet

|

| 0005 | XCT | Utför enkel instruktion: PC ← (SP)+, PS ← (SP)+, ställ in spårningsflagga, kör opkod, -(SP) ← PS, -(SP) ← PC, spårningsflagga återställ, Om inget fel PC ← (0020) ) annat PC ← (001E)

|

| 0006 | BPT | Brytpunktsfälla: -(SP) ← PS, -(SP) ← PC, PC ← (002C)

|

| 0007 | WFI | Vänta på avbrott: Aktivera avbrott (I2 ← 1). Bussverksamheten upphör.

|

| 0008 | RSVC | Återkomst från arbetsledaresamtal (B eller C): REST, SP ← SP + 2, RTT

|

| 0009 | RRTT | Återställ och återvänd från fällan: REST, RTT

|

| 000A | SPARA | Spara register: -(SP) ← R5, -(SP) ← R4, -(SP) ← R3, -(SP) ← R2, -(SP) ← R1, -(SP) ← R0

|

| 000B | SAVS | Spara status: SPARA, -(SP) ← (002E), (002E) ← (002E) ∨ Mask, MSKO, IEN. Obs Mask lagras i det andra instruktionsordet.

|

| 00°C | RESTEN | Återställ register: R0 ← (SP)+, R1 ← (SP)+, R2 ← (SP)+, R3 ← (SP)+, R4 ← (SP)+, R5 ← (SP)+

|

| 000D | RRTN | Återställ och returnera: REST, PC ← (SP)+

|

| 000E | RSTS | Återställ status: (002E) ← (SP)+, MSKO, REST, RTT

|

| 000F | RTT | Retur från fällan: PC ← (SP)+, PS ← (SP)+

|

Arbetsledaren ringer

Dessa instruktioner används för att implementera operativsystem (supervisor) anrop. Alla har ett sexbitars registerargument. SVCB och SVCC är utformade så att ett argument till operativsystemet kan använda de flesta adresseringslägen som stöds av den ursprungliga instruktionsuppsättningen.

| 15 | 6 | 5 | 0 | ||||||||||||

| Opcode | Arg | ||||||||||||||

| Opcode | Mnemonic | Drift |

|---|---|---|

| 0040 | SVCA | Supervisor Call A: -(SP) ← PS ,-(SP) ← PC, PC ← (0022) + Arg × 2, PC ← (PC)

|

| 0080 | SVCB | Arbetsledare Call B: TMPA ← SP, -(SP) ← PS, -(SP) ← PC, TMPB ← SP, -(SP) ← TMPA, -(SP) ← R5, -(SP) ← R4, -(SP) ) ← R3, -(SP) ← R2, -(SP) ← R1, -(SP) ← R0, R1 ← TMPB, R5 ← Arg × 2, PC ← (0024)

|

| 00C0 | SVCB | Arbetsledare Call C: TMPA ← SP, -(SP) ← PS, -(SP) ← PC, TMPB ← SP, -(SP) ← TMPA, -(SP) ← R5, -(SP) ← R4, -(SP) ) ← R3, -(SP) ← R2, -(SP) ← R1, -(SP) ← R0, R1 ← TMPB, R5 ← Arg × 2, PC ← (0026)

|

Tillståndskodoperationer

| 15 | 4 | 3 | 2 | 1 | 0 | ||||||||||

| Opcode | N | Z | V | C | |||||||||||

| Opcode | Mnemonic | Drift |

|---|---|---|

| 0030 | LCC | Belastningsvillkorskoder: Belastning enligt N, Z, V, C bitar

|

De fyra villkorskoderna i processorstatusordet (PSW) är

- N indikerar ett negativt värde

- Z indikerar ett noll (lika) villkor

- V som indikerar ett spilltillstånd , och

- C indikerar ett bärtillstånd .

Reserverade platser med lågt minne

Minnesplatser mellan 0000 och 003F har fasta funktioner definierade av processorn. Alla adresser nedan är ordadresser.

| Vektor | Skick |

|---|---|

| 0000-0010 | R0 - R5, SP, PC och PS för alternativ för start/stopp |

| 0012 | bussfel PC |

| 0014 | icke-vektoravbrott strömavbrott PC |

| 0016 | power up/stopp alternativ strömåterställning PC |

| 0018 | paritetsfel PC |

| 001A | reserverad op-kod PC |

| 001C | olagligt op-kod format PC |

| 001E | XCT-fel PC |

| 0020 | XCT spåra PC |

| 0022 | SVCA-tabelladress |

| 0024 | SVCB PC |

| 0026 | SVCC PC |

| 0028 | vektorerad avbrottstabelladress (I0). |

| 002A | icke-vektoravbrott (I1) PC |

| 002C | BPT PC |

| 002E | I/O-prioritetsavbrottsmask |

| 0030-003C | Flytpunkts-skraplotter |

| 003E | Flyttalsfel PC |

Prestanda

WD16-processorhastigheten varierar beroende på klockhastighet, minneskonfiguration, operationskod och adresseringslägen. Instruktionstidpunkten har upp till tre komponenter, exekvering/hämtning av själva instruktionen och åtkomsttid för källan och destinationen. De två sista komponenterna beror på adresseringsläget. , vid 3,3 MHz, har en instruktion av formen ADD x (Rm ) , y (Rn ) en hämtning/exekveringstid på 3,6 mikrosekunder plus källtid på 3 mikrosekunder och destinationstid på 3,3 mikrosekunder, för en total instruktion tid på 10 mikrosekunder. Register-till-register ADD Rm , Rn exekveras på 3,6 mikrosekunder . Flytpunkten är betydligt långsammare. En enkel och en halv precision (48 bitars) flytande add-instruktion sträcker sig från 60 till 140 mikrosekunder. WD16:s precision är en kompromiss mellan traditionella enkel- och dubbelprecisionsflottörer.

Som kontrast var den snabbaste PDP-11-datorn vid den tiden PDP-11/70. En instruktion av formen ADDx ( Rm ) , y (Rn ) har en hämtning/exekveringstid på 1,35 mikrosekunder plus käll- och destinationstider på 0,6 mikrosekunder vardera, för en total instruktionstid på 2,55 mikrosekunder . Alla fall där adresserat minne inte fanns i cachen lägger till 1,02 mikrosekunder. Register-till-register ADD Rm, Rn kunde exekveras från cachen på 0,3 mikrosekunder . En flytande add-instruktion med enkel precision som exekveras av FP11-C-medprocessorn kan variera från 0,9 till 2,5 mikrosekunder plus tid för att hämta operanderna som kan sträcka sig upp till 4,2 mikrosekunder.

WD16-blocköverföringsinstruktionerna fördubblar ungefär hastigheten för drag och block I/O. Ett ord som flyttas med MOV (R1)+,(R2)+, SOB R0, loop- instruktioner tar 10,6 mikrosekunder per iteration. MBWU R1,R2- ekvivalenten tar 5,3 mikrosekunder per iteration.

Association of Computer Users utförde en serie riktmärken på ett AM-100T-baserat system som kostade 35 680 $ (motsvarande 117 343 $ 2021). De fann att deras CPU-bundna benchmark kördes på 31,4 sekunder på AM-100T jämfört med 218 sekunder för det genomsnittliga enanvändarsystemet i prisklassen $15 000 till $25 000. I en grupp fleranvändardatorer som kostar mellan $25 000 och $50 000, var AM-100T i "övre tredjedelen" för hastighet.

Creative Computing Benchmark från maj 1984 placerade WD16 (i AM-100T-applikationen) som nummer 34 av 183 testade maskiner. Den förflutna tiden var 10 sekunder, jämfört med 24 sekunder för IBM PC .

Emulator

Virtual Alpha Micro är en WD16-emulator med öppen källkod. Skrivet i C, emulerar den WD16-processorn och hårdvarumiljön Alpha Micro AM-100. Författaren hävdar att den körs på Linux (inklusive Raspberry Pi), Windows och Macintosh-datorer, även om inga binärfiler tillhandahålls. Den kommer att köra Alpha Micro Operating System (AMOS) och alla tillhörande program. 2002 gav Alpha Micro begränsat tillstånd att distribuera AMOS 4.x- eller 5.0-binärfiler inklusive manualerna endast för hobbybruk.