Uttag FM2

| |

| Typ | PGA - ZIF |

|---|---|

| Chip formfaktorer | PGA |

| Kontakter | 904 |

| FSB- protokoll | Unified Media Interface (UMI) |

| Företrädare | FM1 |

| Efterträdare | FM2+ |

|

Den här artikeln är en del av CPU-socket -serien | |

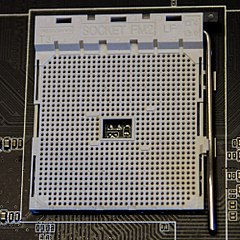

Socket FM2 är ett CPU- uttag som används av AMD :s stationära Trinity och Richland APU:er för att ansluta till moderkortet samt Athlon X2 och Athlon X4 processorer baserade på dem. FM2 lanserades den 27 september 2012. Moderkort som har den då nya FM2 CPU-sockeln använder också AMD:s då nya A85X -chipset.

Sockeln är mycket lik FM1 , baserat på ett 31×31 rutnät av stift med ett 5×7 centralt tomrum, 3 stift saknas i varje hörn och några ytterligare nyckelstift saknas. Jämfört med Socket FM1 flyttades två nyckelstift, och en till tas bort, vilket lämnar 904 stift.

För tillgängliga styrkretsar konsultera Fusion controller hubs (FCH) .

Steamroller -baserade "Kaveri" APU:er stöds inte , se Socket FM2+ (FM2r2) och Socket FP3 (BGA-???).

Kylfläns

De 4 hålen för att fästa kylflänsen på moderkortet är placerade i en rektangel med sidolängder på 48 mm och 96 mm för AMD:s uttag Socket AM2 , Socket AM2+ , Socket AM3 , Socket AM3+ och Socket FM2 . Kyllösningar bör därför vara utbytbara.

Funktionsöversikt

Följande tabell visar funktioner hos AMD :s processorer med 3D-grafik, inklusive APU:er (se även: Lista över AMD-processorer med 3D-grafik ).

| Plattform | Hög, standard och låg effekt | Låg och ultralåg effekt | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Kodnamn | Server | Grundläggande | Toronto | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Micro | Kyoto | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Skrivbord | Prestanda | Raphael | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Vanliga | Llano | Treenighet | Richland | Kaveri | Kaveri Refresh (Godavari) | Carrizo | Bristol Ridge | Raven Ridge | Picasso | Renoir | Cezanne | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Inträde | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Grundläggande | Kabini | Dalí | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Mobil | Prestanda | Renoir | Cezanne | Rembrandt | Dragon Range | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Vanliga | Llano | Treenighet | Richland | Kaveri | Carrizo | Bristol Ridge | Raven Ridge | Picasso |

Renoir Lucienne |

Cezanne Barceló |

Fågel Fenix | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Inträde | Dalí | Mendocino | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Grundläggande | Desna, Ontario, Zacate | Kabini, Temash | Beema, Mullins | Carrizo-L | Stoney Ridge | Pollock | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Inbäddad | Treenighet | Vithövdad havsörn |

Merlin Falcon , Brown Falcon |

Stor hornuggla | Grå hök | Ontario, Zacate | Kabini |

Stäppörn , Crowned Eagle , LX-Familjen |

Prairie Falcon | Bandad tornfalk | River Hawk | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Släppte | augusti 2011 | oktober 2012 | juni 2013 | jan 2014 | 2015 | juni 2015 | juni 2016 | oktober 2017 | jan 2019 | mars 2020 | jan 2021 | jan 2022 | september 2022 | jan 2023 | jan 2011 | Maj 2013 | apr 2014 | maj 2015 | februari 2016 | april 2019 | juli 2020 | juni 2022 | nov 2022 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| CPU mikroarkitektur | K10 | Piledriver | Ångvält | Grävmaskin | " Grävmaskin+ " | Zen | Zen+ | Zen 2 | Zen 3 | Zen 3+ | Zen 4 | Bobcat | Jaguar | Puma | Puma+ | " Grävmaskin+ " | Zen | Zen+ | " Zen 2+ " | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ÄR EN | x86-64 v1 | x86-64 v2 | x86-64 v3 | x86-64 v4 | x86-64 v1 | x86-64 v2 | x86-64 v3 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Uttag | Skrivbord | Prestanda | — | AM5 | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Vanliga | — | AM4 | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Inträde | FM1 | FM2 | FM2+ | FM2+ , AM4 | AM4 | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Grundläggande | — | — | AM1 | — | FP5 | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Övrig | FS1 | FS1+ , FP2 | FP3 | FP4 | FP5 | FP6 | FP7 | ? | ? | FT1 | FT3 | FT3b | FP4 | FP5 | FT5 | FP5 | FT6 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| PCI Express- version | 2.0 | 3.0 | 4.0 | 5.0 | 4.0 | 2.0 | 3.0 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| CXL | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Fab. ( nm ) |

GF 32SHP ( HKMG SOI ) |

GF 28SHP (HKMG bulk) |

GF 14LPP ( FinFET bulk) |

GF 12LP (FinFET bulk) |

TSMC N7 (FinFET bulk) |

TSMC N6 (FinFET bulk) |

CCD: TSMC N5 (FinFET bulk) cIOD: TSMC N6 (FinFET bulk) |

TSMC 4nm (FinFET bulk) |

TSMC N40 (bulk) |

TSMC N28 (HKMG bulk) |

GF 28SHP (HKMG bulk) |

GF 14LPP ( FinFET bulk) |

GF 12LP (FinFET bulk) |

TSMC N6 (FinFET bulk) |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Formarea (mm 2 ) | 228 | 246 | 245 | 245 | 250 | 210 | 156 | 180 | 210 |

CCD: (2x) 70 cIOD: 122 |

178 | 75 (+ 28 FCH ) | 107 | ? | 125 | 149 | ~100 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Min TDP (W) | 35 | 17 | 12 | 10 | 15 | 105 | 35 | 4.5 | 4 | 3,95 | 10 | 6 | 12 | 8 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max APU TDP (W) | 100 | 95 | 65 | 45 | 170 | 54 | 18 | 25 | 6 | 54 | 15 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max lager APU basklocka (GHz) | 3 | 3.8 | 4.1 | 4.1 | 3.7 | 3.8 | 3.6 | 3.7 | 3.8 | 4.0 | 3.3 | 4.7 | 4.3 | 1,75 | 2.2 | 2 | 2.2 | 3.2 | 2.6 | 1.2 | 3,35 | 2.8 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max APU per nod | 1 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max kärndör per CPU | 1 | 2 | 1 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max CCX per kärnform | 1 | 2 | 1 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max kärnor per CCX | 4 | 8 | 2 | 4 | 2 | 4 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max CPU -kärnor per APU | 4 | 8 | 16 | 8 | 2 | 4 | 2 | 4 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max trådar per CPU-kärna | 1 | 2 | 1 | 2 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Heltals pipelinestruktur | 3+3 | 2+2 | 4+2 | 4+2+1 | 1+3+3+1+2 | 1+1+1+1 | 2+2 | 4+2 | 4+2+1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| i386, i486, i586, CMOV, NOPL, i686, PAE , NX bit , CMPXCHG16B, AMD-V , RVI , ABM och 64-bitars LAHF/SAHF |

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| IOMMU | — | v2 | v1 | v2 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| BMI1 , AES-NI , CLMUL och F16C | — |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| MOVBE | — |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| AVIC , BMI2 , RDRAND och MWAITX/MONITORX | — |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| SME , TSME , ADX , SHA , RDSEED , SMAP , SMEP , XSAVEC, XSAVES, XRSTORS, CLFLUSHOPT, CLZERO och PTE Coalescing | — |

|

— |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| GMET , WBNOINVD, CLWB, QOS, PQE-BW, RDPID, RDPRU och MCOMMIT | — |

|

— |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| MPK , VAES | — |

|

— | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| SGX | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| FPU per kärna | 1 | 0,5 | 1 | 1 | 0,5 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Rör per FPU | 2 | 2 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| FPU rörbredd | 128-bitars | 256-bitars | 80-bitars | 128-bitars | 256-bitars | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| CPU- instruktionsuppsättning SIMD- nivå | SSE4a | AVX | AVX2 | AVX-512 | SSSE3 | AVX | AVX2 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 3DNu! | 3DNow!+ | — | — | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| PREFETCH/PREFETCHW |

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| GFNI | — |

|

— | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| AMX | — | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| FMA4 , LWP, TBM och XOP | — | — | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| FMA3 |

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| AMD XDNA | — |

|

— | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| L1- datacache per kärna (KiB) | 64 | 16 | 32 | 32 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| L1 datacacheassociativitet (sätt ) | 2 | 4 | 8 | 8 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| L1-instruktionscacher per kärna | 1 | 0,5 | 1 | 1 | 0,5 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max APU totalt L1-instruktionscache (KiB) | 256 | 128 | 192 | 256 | 512 | 256 | 64 | 128 | 96 | 128 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| L1-instruktionscacheassociativitet (sätt ) | 2 | 3 | 4 | 8 | 2 | 3 | 4 | 8 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| L2 cacher per kärna | 1 | 0,5 | 1 | 1 | 0,5 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max APU totalt L2-cache (MiB) | 4 | 2 | 4 | 16 | 1 | 2 | 1 | 2 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| L2-cacheassociativitet ( sätt) | 16 | 8 | 16 | 8 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max on--die L3 cache per CCX (MiB) | — | 4 | 16 | 32 | — | 4 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max 3D V-cache per CCD (MiB) | — | 64 | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max total cache i-CCD L3 per APU (MiB) | 4 | 8 | 16 | 64 | 4 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max. totalt 3D V-cache per APU (MiB) | — | 64 | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max. kort L3-cache per APU (MiB) | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max total L3-cache per APU (MiB) | 4 | 8 | 16 | 128 | 4 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| APU L3-cacheassociativitet ( sätt) | 16 | 16 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| L3 cache-schema | Offer | Offer | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max. L4 cache | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max lager DRAM- stöd | DDR3 -1866 | DDR3-2133 | DDR3-2133, DDR4 -2400 | DDR4-2400 | DDR4-2933 | DDR4-3200, LPDDR4 -4266 | DDR5 -4800, LPDDR5 -6400 | DDR5 -5200 | DDR5 -5600, LPDDR5x -7500 | DDR3L -1333 | DDR3L-1600 | DDR3L-1866 | DDR3-1866, DDR4 -2400 | DDR4-2400 | DDR4-1600 | DDR4-3200 | LPDDR5-5500 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max DRAM- kanaler per APU | 2 | 1 | 2 | 1 | 2 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max lager DRAM- bandbredd (GB/s) per APU | 29,866 | 34,132 | 38.400 | 46,932 | 68,256 | 102.400 | 83.200 | 120 000 | 10,666 | 12.800 | 14,933 | 19.200 | 38.400 | 12.800 | 51.200 | 88 000 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| GPU mikroarkitektur | TeraScale 2 (VLIW5) | TeraScale 3 (VLIW4) | GCN 2:a gen | GCN 3:e gen | GCN 5:e gen | RDNA 2:a gen | RDNA 3:e gen | TeraScale 2 (VLIW5) | GCN 2:a gen | GCN 3:e gen | GCN 5:e gen | RDNA 2:a gen | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| GPU- instruktionsuppsättning | TeraScale instruktionsuppsättning | GCN-instruktionsuppsättning | RDNA-instruktionsuppsättning | TeraScale instruktionsuppsättning | GCN-instruktionsuppsättning | RDNA-instruktionsuppsättning | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max lager GPU basklocka (MHz) | 600 | 800 | 844 | 866 | 1108 | 1250 | 1400 | 2100 | 2400 | 400 | 538 | 600 | ? | 847 | 900 | 1200 | 600 | 1300 | 1900 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max lager GPU bas GFLOPS | 480 | 614,4 | 648,1 | 886,7 | 1134,5 | 1760 | 1971.2 | 2150,4 | 3686,4 | 102,4 | 86 | ? | ? | ? | 345,6 | 460,8 | 230,4 | 1331,2 | 486,4 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 3D-motor | Upp till 400:20:8 | Upp till 384:24:6 | Upp till 512:32:8 | Upp till 704:44:16 | Upp till 512:32:8 | 768:48:8 | 128:?:? | 80:8:4 | 128:8:4 | Upp till 192:12:8 | Upp till 192:12:4 | 192:12:4 | Upp till 512:?:? | 128:?:? | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| IOMMUv1 | IOMMUv2 | IOMMUv1 | ? | IOMMUv2 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Videoavkodare | UVD 3.0 | UVD 4.2 | UVD 6.0 | VCN 1.0 | VCN 2.1 | VCN 2.2 | VCN 3.1 | ? | UVD 3.0 | UVD 4.0 | UVD 4.2 | UVD 6.0 | UVD 6.3 | VCN 1.0 | VCN 3.1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Videokodare | — | VCE 1.0 | VCE 2.0 | VCE 3.1 | — | VCE 2.0 | VCE 3.1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| AMD Fluid Motion |

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| GPU energibesparing | Maktspel | PowerTune | Maktspel | PowerTune | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| TrueAudio | — |

|

? | — |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| FreeSync |

1 2 |

1 2 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| HDCP | ? | 1.4 | 2.2 | 2.3 | ? | 1.4 | 2.2 | 2.3 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Spelklar | — | 3.0 inte än | — | 3.0 inte än | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Skärmar som stöds | 2–3 | 2–4 | 3 |

3 (dator) 4 (mobil, inbäddad) |

4 | 2 | 3 | 4 | 4 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

/drm/radeon

|

— | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

/drm/amdgpu

|

— |

|

— |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

externa länkar

- btarunr (2011-07-25). "AMD:s nästa generation Korona avancerade skrivbordsplattform för att smälta processor med Northbridge" . TechPowerUp .

- "APU依然当家 AMD明年各平台产品线曝光" .