Sidstorleksförlängning

Inom datorer hänvisar PSE ( Page Size Extension ) till en funktion hos x86 -processorer som tillåter sidor större än den traditionella storleken på 4 KiB . Den introducerades i den ursprungliga Pentium- processorn, men den dokumenterades endast offentligt av Intel när Pentium Pro släpptes . CPUID - instruktionen kan användas för att identifiera tillgängligheten för PSE på x86- processorer .

Motivering

Föreställ dig följande scenario. Ett applikationsprogram begär ett 1 MiB minnesblock. För att uppfylla denna begäran kommer ett operativsystem som stöder personsökning och som körs på äldre x86 -processorer att behöva allokera 256 sidor om 4 KiB vardera. En overhead på 1 KiB minne krävs för att underhålla sidkataloger och sidtabeller.

Vid åtkomst till detta 1 MiB-minne, skulle var och en av de 256 sidposterna cachelagras i översättnings-lookaside-bufferten (TLB; en cache som kommer ihåg virtuell adress till fysisk adressöversättningar för snabbare uppslag på efterföljande minnesförfrågningar). Att belamra TLB är möjligen en av de största nackdelarna med att ha flera sidposter för vad som kunde ha allokerats i ett enda minnesblock. Om TLB fylls, då skulle en TLB-post behöva frigöras, sidkatalogen och sidtabellerna skulle behöva "vandras" i minnet, och slutligen skulle minnet kommas åt och den nya posten skulle föras in i TLB . Detta är en allvarlig prestationsstraff och var möjligen den största motivationen för att utöka x86-arkitekturen med större sidstorlekar.

PSE tillåter sidstorlekar på 4 MiB att existera tillsammans med 4 KiB sidor. Den 1 MiB-begäran som beskrivits tidigare skulle lätt kunna uppfyllas med en enda 4 MiB-sida, och den skulle bara kräva en TLB-post. Nackdelen med att använda större sidstorlekar är dock intern fragmentering .

Drift

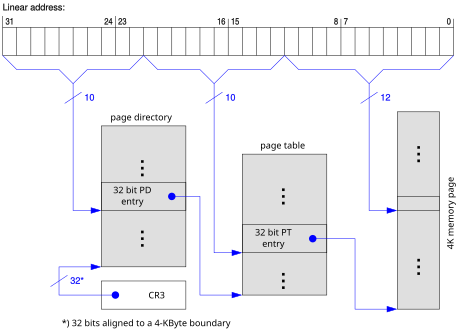

I traditionellt 32-bitars skyddat läge använder x86-processorer ett översättningsschema på två nivåer, där kontrollregistret CR3 pekar på en enda 4 KiB-lång sidkatalog , som är uppdelad i 1024 × 4-byte-poster som pekar på 4 KiB -långa sidtabeller , på liknande sätt bestående av 1024 × 4-byte poster som pekar på 4 KiB-långa sidor.

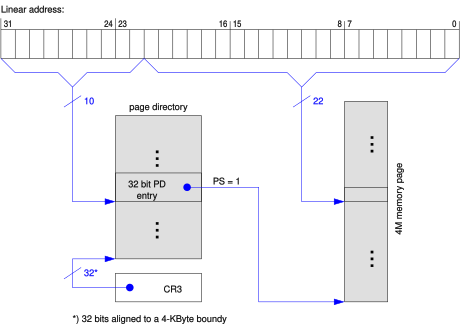

Aktivering av PSE (genom att sätta bit 4, PSE , i systemregistret CR4 ) ändrar detta schema. Posterna i sidkatalogen har en extra flagga, i bit 7, som heter PS (för sidstorlek ) . Denna flagga ignorerades utan PSE, men nu pekar sidkatalogposten med PS inställd på 1 inte till en sidtabell, utan till en enda stor 4 MiB-sida. Sidkatalogposten med PS inställd på 0 beter sig som utan PSE.

Om nyare PSE-36- kapacitet är tillgänglig på CPU, som kontrolleras med CPUID- instruktionen, används ytterligare 4 bitar, utöver normala 10 bitar, inuti en sidkatalogpost som pekar på en stor sida. Detta gör att en stor sida kan placeras i 36-bitars adressutrymme.

Om Physical Address Extension (PAE) används reduceras storleken på stora sidor från 4 MiB ner till 2 MiB, och PSE är alltid aktiverat, oavsett PSE-biten i CR4 .

externa länkar

- Intel 64 och IA-32 Architectures Software Developer's Manuals

- Förstå 4M sidstorleksförlängningar på Pentium-processorn ( Robert R. Collins)