Pentium Pro

| |

| Allmän information | |

|---|---|

| Lanserades | 1 november 1995 |

| Avvecklad | juni 1998 |

| Vanliga tillverkare | |

| Prestanda | |

| Max. CPU klockfrekvens | 150 MHz till 200 MHz |

| FSB- hastigheter | 60 MHz till 66 MHz |

| Arkitektur och klassificering | |

| Tekniknod | 0,35 μm till 0,50 μm |

| Mikroarkitektur | P6 |

| Instruktionsuppsättning | x86 |

| Fysiska specifikationer | |

| Kärnor |

|

| Uttag | |

| Historia | |

| Företrädare | Pentium |

| Efterträdare | Pentium II , Pentium II Xeon |

| Supportstatus | |

| Stöds inte | |

Pentium Pro är en sjätte generationens x86- mikroprocessor utvecklad och tillverkad av Intel och introducerades den 1 november 1995. Den introducerade P6-mikroarkitekturen (ibland kallad i686) och var ursprungligen avsedd att ersätta den ursprungliga Pentium i en hel rad applikationer. Medan Pentium och Pentium MMX hade 3,1 respektive 4,5 miljoner transistorer , innehöll Pentium Pro 5,5 miljoner transistorer. Senare reducerades den till en mer snäv roll som server och avancerad stationär processor och användes i superdatorer som ASCI Red , den första datorn att nå triljonen flyttalsoperationer per sekund (tera FLOPS ) prestandamärke. Pentium Pro kunde ha både dubbel- och fyrprocessorkonfigurationer. Den kom bara i en formfaktor, den relativt stora rektangulära Socket 8 . Pentium Pro efterträddes av Pentium II Xeon 1998.

Mikroarkitektur

Pentium Pros ledande arkitekt var Fred Pollack som var specialiserad på superskalaritet och hade även arbetat som ledande ingenjör för Intel iAPX 432 .

Sammanfattning

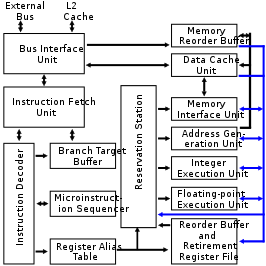

Pentium Pro inkorporerade en ny mikroarkitektur som skiljer sig från Pentiums P5- mikroarkitektur. Den har en frikopplad, 14-stegs superpipelined arkitektur som använde en instruktionspool. Pentium Pro ( P6 ) implementerade många radikala arkitektoniska skillnader som speglade andra samtida x86- designer som NexGen Nx586 och Cyrix 6x86 . Pentium Pro-pipelinen hade extra avkodningssteg för att dynamiskt översätta IA-32 -instruktioner till buffrade mikrooperationssekvenser som sedan kunde analyseras, ordnas om och döpas om för att upptäcka parallelliserbara operationer som kan skickas till mer än en exekveringsenhet samtidigt. Pentium Pro presenterade således exekvering i oordning , inklusive spekulativ exekvering via registerbyte . Den hade också en bredare 36-bitars adressbuss , användbar av Physical Address Extension (PAE), vilket gjorde att den fick tillgång till upp till 64 GB minne.

Pentium Pro har en instruktionscache på 8 KB , från vilken upp till 16 byte hämtas på varje cykel och skickas till instruktionsavkodarna . Det finns tre instruktionsavkodare. Avkodarna är olika i förmåga: endast en kan avkoda valfri x86-instruktion, medan de andra två bara kan avkoda enkla x86-instruktioner. Detta begränsar Pentium Pros förmåga att avkoda flera instruktioner samtidigt, vilket begränsar superskalär exekvering. x86-instruktioner avkodas till 118-bitars mikrooperationer (micro-ops). Mikrooperationerna är reducerade instruktionsuppsättningar dator (RISC)-liknande; det vill säga de kodar en operation, två källor och en destination. Den allmänna avkodaren kan generera upp till fyra mikrooperationer per cykel, medan de enkla avkodarna kan generera en mikrooperation vardera per cykel. Således kan x86-instruktioner som fungerar på minnet (t.ex. lägg till detta register till denna plats i minnet) endast bearbetas av den allmänna avkodaren, eftersom denna operation kräver minst tre mikrooperationer. Likaså är de enkla avkodarna begränsade till instruktioner som kan översättas till en mikrooperation. Instruktioner som kräver fler mikrooperationer än fyra översätts med hjälp av en sequencer, som genererar de nödvändiga mikrooperationerna över flera klockcykler. Pentium Pro var den första processorn i x86-familjen som stödde uppgraderingsbar mikrokod under BIOS och/eller operativsystem (OS) kontroll.

Mikrooperationer lämnar omordningsbufferten (ROB) och går in i en reservstation (RS), där de väntar på utskick till exekveringsenheterna. I varje klockcykel kan upp till fem mikrooperationer skickas till fem exekveringsenheter. Pentium Pro har totalt sex exekveringsenheter: två heltalsenheter, en flyttalsenhet (FPU), en belastningsenhet, lagringsadressenhet och en lagringsdataenhet. En av heltalsenheterna delar samma portar som FPU:n, och därför kan Pentium Pro bara skicka en heltalsmikrooperation och en flyttalsmikrooperation, eller två heltalsmikrooperationer per cykel, förutom mikrooperationer. ops för de andra tre avrättningsenheterna. Av de två heltalsenheterna är det bara den som delar sökvägen med FPU:n på port 0 som har det fulla komplementet av funktioner som en tunnskiftare , multiplikator, delare och stöd för LEA-instruktioner. Den andra heltalsenheten, som är ansluten till port 1, har inte dessa faciliteter och är begränsad till enkla operationer såsom addera, subtrahera och beräkning av grenmåladresser.

FPU:n utför flyttalsoperationer. Addition och multiplikation är pipelined och har en latens på tre respektive fem cykler. Division och kvadratrot är inte pipelined och exekveras i separata enheter som delar FPU:s portar. Division och kvadratrot har en latens på 18-36 respektive 29-69 cykler. Det minsta talet är för enstaka precision (32-bitars) flyttal och det största för utökad precision (80-bitars) tal. Division och kvadratrot kan arbeta samtidigt med addering och multiplikation, vilket hindrar dem från att utföras endast när resultatet måste lagras i ROB.

Efter att mikroprocessorn släppts upptäcktes en bugg i flyttalsenheten , vanligen kallad "Pentium Pro och Pentium II FPU bugg" och av Intel som "flagga erratum". Felet uppstår under vissa omständigheter under flyttal-till-heltalskonvertering när flyttalsnumret inte passar in i det mindre heltalsformatet, vilket gör att FPU:n avviker från sitt dokumenterade beteende. Felet anses vara mindre och inträffar under så speciella omständigheter att mycket få, om några, program påverkas.

Pentium Pro P6-mikroarkitekturen användes i en eller annan form av Intel i mer än ett decennium. Pipelinen skulle skalas från den första 150 MHz-starten, hela vägen upp till 1,4 GHz med "Tualatin" Pentium III . Designens olika egenskaper skulle fortsätta efter det i den härledda kärnan som kallas " Banias " i Pentium M och Intel Core ( Yonah ), som i sig skulle utvecklas till Core-mikroarkitekturen ( Core 2- processor) 2006 och framåt.

Instruktionsuppsättning

Pentium Pro (P6) introducerade nya instruktioner i Intel-sortimentet; CMOVxx-instruktionerna ('villkorlig flyttning') kan flytta ett värde som antingen är innehållet i ett register eller minnesplats till ett annat register eller inte, enligt något logiskt predikatvillkor xx i flaggregistret, där xx är en flaggpredikatskod som given i villkoret för villkorliga hoppanvisningar. Så till exempel flyttar CMOVNE ett specificerat värde in i ett register eller inte beroende på om NE (icke-lika)-villkoret är sant i flaggregistret, dvs. Z-flagga = 0. Detta tillåter utvärdering av om-då-annas-operationer och till exempel den ? : drift i C. Dessa instruktioner ger en prestandaökning genom att tillåta undvikande av kostsamma hopp- och greninstruktioner. I t.ex. CMOVxx destreg1, source_operand2 är den första operanden destinationsregistret, den andra källregistret eller minnesplatsen. Den andra operanden kan tyvärr inte vara ett omedelbart (in-line konstant) värde och en sådan konstant måste placeras i ett register först. Predikatkoden xx kan ta hela området av värden som tillåts i villkorliga grenar.

En andra utveckling var dokumentationen av den olagliga UD2-instruktionen. Denna op-kod är reserverad och garanterat orsaka ett olagligt instruktionsundantag på P6 och alla senare processorer. Detta gör att utvecklare enkelt kan krascha det aktuella programmet på ett framtidssäkert sätt när en bugg upptäcks av programvara.

Prestanda

Trots att den var avancerad för tiden hade Pentium Pro:s out-of-order register byta arkitektur problem med att köra 16-bitars kod och blandad kod ( 8-bitars med 16-bitars (8/16), eller 16-bitars med 32-bitars (16/32), eftersom användning av partiella register orsakar frekvent spolning av pipeline. Specifik användning av partiella register var då en vanlig prestandaoptimering, eftersom det inte medförde någon prestandastraff på pre-P6 Intel-processorer; även de dominerande operativsystemen vid tidpunkten för Pentium Pros utgåva var 16-bitars DOS och blandade 16/32-bitars Windows 3.1x och Windows 95 (även om det senare kräver en 32-bitars 80386 CPU, är mycket av dess kod fortfarande 16-bitars av prestandaskäl, som t.ex. USER.exe ). Detta, med de höga kostnaderna för Pentium Pro-system, ledde till ljummet försäljning bland PC-köpare vid den tiden. För att fullt ut använda Pentium Pro:s P6-mikroarkitektur behövs ett helt 32-bitars operativsystem, som Windows NT , Linux , Unix eller OS/2 . Prestandaproblemen på äldre kod mildrades senare delvis av Intel med Pentium II.

Jämfört med RISC-mikroprocessorer överträffade Pentium Pro, när den introducerades, något bättre än de snabbaste RISC-mikroprocessorerna när det gäller heltalsprestanda när man körde SPECint95-riktmärket, men flyttalsprestanda var betydligt lägre, hälften av vissa RISC-mikroprocessorer. Pentium Pro:s heltalsprestandaförsprång försvann snabbt, först omkörd av MIPS Technologies R10000 i januari 1996, och sedan av Digital Equipment Corporations EV56-variant av Alpha 21164 .

Recensenter noterade snabbt de mycket långsamma skrivningarna till videominnet som den svaga punkten för P6-plattformen, med prestanda här som är så låg som 10 % av ett identiskt klockat Pentium-system i benchmarks som VIDSPEED. Metoder för att kringgå detta inkluderade att ställa in VESA-ritning till systemminne istället för videominne i spel som Quake , och senare uppstod verktyg som FASTVID, som kunde fördubbla prestandan i vissa spel genom att möjliggöra skrivkombinationsfunktionerna hos CPU:n. [ död länk ] register för minnestyp (MTRR) ställs in automatiskt av Windows-videodrivrutiner från ~1997, och där fick det förbättrade cache-/minnesundersystemet och FPU-prestanda det att utklassa Pentium klocka-för-klocka i de framväxande 3D-spelen från mitten till slutet av 1990-talet, särskilt när man använder NT4. Dess avsaknad av MMX- implementering minskar dock prestandan i multimediaapplikationer som använde dessa instruktioner.

Cachning

L2-cache på paketet, som sträckte sig från 256 KB vid introduktionen till 1 MB 1997. På den tiden tillät tillverkningstekniken inte på ett praktiskt sätt en stor L2-cache att integreras i processorkärnan. Intel placerade istället L2-formarna separat i paketet vilket fortfarande gjorde att den kunde köras med samma klockhastighet som CPU-kärnan. Dessutom, till skillnad från de flesta moderkortsbaserade cache-scheman som delade huvudsystembussen med processorn, hade Pentium Pros cache sin egen baksida buss (kallad dual independent bus av Intel). På grund av detta kunde processorn läsa huvudminnet och cache samtidigt, vilket kraftigt minskade en traditionell flaskhals. Cachen var också "icke-blockerande", vilket innebär att processorn kunde utfärda mer än en cachebegäran åt gången (upp till 4), vilket minskade påföljder för cachemissar. (Detta är ett exempel på MLP, Memory Level Parallelism .) Dessa egenskaper kombinerades för att producera en L2-cache som var oerhört snabbare än moderkortsbaserade cachar för äldre processorer. Bara denna cache gav processorn en fördel i in-/utgångsprestanda jämfört med äldre x86 -processorer. I multiprocessorkonfigurationer höjde Pentium Pros integrerade cache prestandan i höjden jämfört med arkitekturer där varje CPU delade en central cache.

Men denna mycket snabbare L2-cache kom med vissa komplikationer. Pentium Pros "on-package cache"-arrangemang var unikt. Processorn och cachen låg på separata dies i samma paket och tätt sammankopplade med en fullhastighetsbuss. De två eller tre formarna måste bindas samman tidigt i produktionsprocessen, innan testning var möjlig. Detta innebar att ett enda, litet fel i endera formen gjorde det nödvändigt att kassera hela enheten, vilket var en av anledningarna till Pentium Pro:s relativt låga produktionsutbyte och höga kostnad. Alla versioner av chipet var dyra, särskilt de med 1024 KB, eftersom det krävde två 512 KB cache-dödar samt processormatrisen.

Tillgängliga modeller

Pentium Pro klockhastigheter var 150, 166, 180 eller 200 MHz med en extern bussklocka på 60 eller 66 MHz. Vissa användare valde att överklocka sina Pentium Pro-chips, där 200 MHz-versionen ofta körs på 233 MHz, 180 MHz-versionen ofta körs på 200 MHz och 150 MHz-versionen ofta körs på 166 MHz. Chipet var populärt i symmetriska multiprocessorkonfigurationer, med dubbla och fyrkantiga SMP-server- och arbetsstationsinställningar var vanliga.

I Intels "Familj/Model/Stepping"-schema är Pentium Pro familj 6, modell 1, och dess Intel-produktkod är 80521.

| Klocka | Buss | L2-cache | Max TDP |

|---|---|---|---|

| 150 MHz | 60 MHz | 256 KB | 29,2 W |

| 166 MHz | 66 MHz | 512 KB | 35 W |

| 180 MHz | 60 MHz | 256 KB | 31,7 W |

| 200 MHz | 66 MHz | 35 W | |

| 512 KB | 37,9 W | ||

| 1024 KB | 44 W |

Tillverkning

Processen som användes för att tillverka Pentium Pro-processormatrisen och dess separata cacheminnesmatris ändrades, vilket ledde till en kombination av processer som används i samma paket:

- 133 MHz Pentium Pro-prototypprocessormatrisen tillverkades i en 0,6 μm BiCMOS-process.

- 150 MHz Pentium Pro-processormatrisen tillverkades i en 0,50 μm BiCMOS- process.

- 166, 180 och 200 MHz Pentium Pro-processormatrisen tillverkades i en 0,35 μm BiCMOS-process.

- 256 KB L2-cache-matrisen tillverkades i en 0,50 μm BiCMOS-process.

- 512 och 1024 KB L2-cache-matrisen tillverkades i en 0,35 μm BiCMOS-process.

Förpackning

Pentium Pro (upp till 512 KB cache) är förpackad i en keramisk multichipmodul (MCM). MCM:n innehåller två hålrum på undersidan där mikroprocessormatrisen och dess följeslagare finns. Formarna är bundna till en värmeklump, vars exponerade topp hjälper värmen från formarna att överföras mer direkt till kylapparater såsom en kylfläns. Formarna är anslutna till förpackningen med hjälp av konventionell trådbindning. Hålrummen är täckta med en keramisk platta.

Pentium Pro med 1 MB cache använder en plast-MCM. Istället för två hålrum finns det bara en, i vilken de tre formarna finns, bunden till förpackningen istället för en värmeklump. Hålrummen är fyllda med epoxi.

MCM har 387 stift, varav ungefär hälften är anordnade i en pingrid array (PGA) och hälften i en interstitial pin grid array (IPGA). Förpackningen är designad för Socket 8 .

Uppgradera vägar

1998 släpptes 300/333 MHz Pentium II Overdrive- processorn för Socket 8. Med dubbel L1 och 512 KB fullhastighets L2-cache, producerades den av Intel som ett drop-in-uppgraderingsalternativ för ägare av Pentium Pro-system. Den stödde dock bara tvåvägs limfri multiprocessing, inte fyrvägs eller högre, vilket inte gjorde det till en användbar uppgradering för fyrprocessorsystem. Dessa specialpaketerade Pentium II Xeon-processorer användes för att uppgradera ASCI Red , som blev den första datorn att nå teraFLOPS-prestandamärket med Pentium Pro-processorn och sedan den första som översteg 2 teraFLOPS efter uppgraderingen till Pentium II Xeon-processorer.

När Slot 1- moderkort blev vanliga släppte flera tillverkare socketadaptrar , som Tyan M2020, Asus C-P6S1, Tekram P6SL1 och Abit KP6. Socklarna gjorde att Pentium Pro-processorer kunde användas med Slot 1-moderkort. Intel 440FX -kretsuppsättningen stödde uttryckligen både Pentium Pro- och Pentium II-processorer, men Intel 440BX och senare Slot 1-kretsuppsättningar stödde inte uttryckligen Pentium Pro, så Socket 8-socketarna såg inte någon stor användning. Slockets, i form av Socket 370 till Slot 1-adaptrar, såg förnyad popularitet när Intel introducerade Socket 370 Celeron och Pentium III- processorer.

Kärnspecifikationer

Pentium Pro

- L1-cache : 8, 8 KB (data, instruktioner)

- L2-cache : 256, 512 KB (en dies) eller 1024 KB (två 512 KB dies) i en multichipmodul klockad med CPU-hastighet

- Sockel: Sockel 8

- Front-side buss : 60 och 66 MHz

- VCore: 3,1–3,3 V

- Tillverkning: 0,50 μm eller 0,35 BiCMOS

- Klockfrekvens: 150, 166, 180, 200 MHz, (kan vara 233 MHz på vissa moderkort)

- Första release: november 1995

Pentium II Overdrive

- L1-cache: 16, 16 KB (data + instruktioner)

- L2-cache: 512 KB externt chip på CPU-modulen klockad med CPU-hastighet

- Sockel: Sockel 8

- Multiplikator: Låst på 5×

- Front-side buss: 60 och 66 MHz

- VCore: 3,1–3,3 V (har inbyggd spänningsregulator)

- Tillverkning: 0,25 μm

- Clockrate: Baserat på Deschutes -generationen Pentium II

- Första utgåvan: 1997

- Stöder MMX- teknik

Buss- och multiprocessorkapacitet

Pentium Pro använde GTL+ -signalering i sin främre buss. Pentium Pro kan användas av sig själv i upp till fyrvägsdesign. Åttavägs Pentium Pro-datorer byggdes också, men dessa använde flera bussar.

Designen av Pentium Pro-bussen påverkades av Futurebus , Intel iAPX 432- bussen och delar av Intel i960- bussen. Futurebus har varit tänkt som en avancerad buss för att ersätta VMEbus som användes med Motorola 68000 från slutet av 1970-talet, men den stagnerade i standardiseringskommittén i mer än ett decennium om man räknar alla vändningar. Intels iAPX 432-initiativ var också ett kommersiellt misslyckande, men i processen lärde de sig hur man bygger en delad transaktionsbuss för att stödja ett cachelöst multiprocessorsystem. i960 hade vidareutvecklat den delade transaktionsbussen iAPX 432 för att inkludera ett cache-koherensprotokoll, vilket slutade med en funktionsuppsättning som mycket påminner om de ursprungliga Futurebus-ambitionerna.

Ledararkitekten för i960 var superskalaritetsspecialisten Fred Pollack som också var huvudingenjören av Intel iAPX 432 och huvudarkitekten för i686-chippet, Pentium Pro. Han var utan tvekan välbekant med hela denna historia. Pentium Pro designades för att inkludera den 4-vägs SMP-delad transaktion cache-koherent buss som en obligatorisk funktion för varje chip som produceras. Detta tjänade också till att neka konkurrenter tillgång till socket för att producera klonade processorer.

Även om Pentium Pro inte var framgångsrik som en maskin för massorna, på grund av dåligt 16-bitarsstöd för Windows 95, blev den mycket framgångsrik i filserverutrymmet på grund av dess avancerade, integrerade bussdesign, som introducerade många avancerade funktioner som hade tidigare bara varit tillgängligt i det dyra arbetsstationssegmentet på råvarumarknaden.

Pentium Pro/6:e generationens konkurrenter

- AMD K5 och K6

- Cyrix 6x86 och MII

- IDT WinChip

- Intel P5 Pentium , samexisterade med Pentium Pro i flera år

Se även

externa länkar

- Backside Bus , searchstorage.techtarget.com

- Intel Pentium Pro-bilder och beskrivningar , cpu-collection.de

- CPU-INFO: Intel Pentium Pro, djupgående processorhistorik , web.archive.org