MSI-protokoll

Inom datorer fungerar MSI -protokollet - ett grundläggande cache-koherensprotokoll - i multiprocessorsystem. Som med andra cachekoherensprotokoll identifierar bokstäverna i protokollnamnet de möjliga tillstånden i vilka en cache-linje kan vara.

Översikt

I MSI kan varje block som finns i en cache ha ett av tre möjliga tillstånd:

- Ändrad : Blocket har ändrats i cachen . Datan i cachen är då inkonsistent med stödlagret (t.ex. minne ). En cache med ett block i "M"-tillståndet har ansvaret att skriva blocket till stödarkivet när det vräkts.

- Delat : Detta block är oförändrat och finns i skrivskyddat läge i minst en cache. Cachen kan avhysa data utan att skriva den till backup-arkivet.

- I nvalid: Detta block finns antingen inte i den aktuella cachen eller har ogiltigförklarats av en bussförfrågan och måste hämtas från minnet eller en annan cache om blocket ska lagras i denna cache.

Dessa koherenstillstånd upprätthålls genom kommunikation mellan cacharna och stödlagret. Cacharna har olika ansvar när block läses eller skrivs, eller när de får reda på andra cachar som utfärdar läser eller skrivningar för ett block.

När en läsbegäran anländer till en cache för ett block i "M"- eller "S"-tillstånden, tillhandahåller cachen data. Om blocket inte är i cachen (i "I"-tillståndet), måste det verifiera att blocket inte är i "M"-tillståndet i någon annan cache. Olika cachningsarkitekturer hanterar detta på olika sätt. Bussarkitekturer utför till exempel ofta snooping , där läsbegäran sänds till alla cachar. Andra arkitekturer inkluderar cachekataloger som har agenter (kataloger) som vet vilka cacher som senast hade kopior av ett visst cacheblock. Om en annan cache har blocket i "M"-tillståndet, måste det skriva tillbaka data till backing-lagringen och gå till "S"- eller "I"-tillstånden. När väl vilken "M"-rad som helst har skrivits tillbaka, erhåller cachen blocket från antingen stödminnet eller en annan cache med data i "S"-tillståndet. Cachen kan sedan tillhandahålla data till den som begär det. Efter att ha tillhandahållit data är cacheblocket i "S"-tillståndet.

När en skrivbegäran kommer till en cache för ett block i "M"-tillståndet, modifierar cachen data lokalt. Om blocket är i "S"-tillståndet måste cachen meddela alla andra cacher som kan innehålla blocket i "S"-tillståndet att de måste vräka blocket. Detta meddelande kan ske via busssnokning eller en katalog, enligt beskrivningen ovan. Då kan data ändras lokalt. Om blocket är i "I"-tillståndet, måste cachen meddela alla andra cacher som kan innehålla blocket i "S"- eller "M"-tillstånden att de måste vräka blocket. Om blocket är i en annan cache i "M"-tillståndet, måste den cachen antingen skriva data till backing-lagringen eller tillhandahålla den till den begärande cachen. Om vid denna tidpunkt cachen ännu inte har blocket lokalt, läses blocket från backing-lagringen innan det modifieras i cachen. Efter att data har modifierats är cacheblocket i "M"-tillståndet.

För ett givet par cacher är de tillåtna tillstånden för en given cache-linje följande:

| M | S | jag | |

|---|---|---|---|

| M |

|

|

|

| S |

|

|

|

| jag |

|

|

|

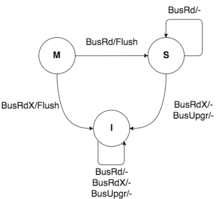

Statsmaskin

Processorförfrågningar till cachen inkluderar:

- PrRd: Processorbegäran att läsa ett cacheblock.

- PrWr: Processorbegäran att skriva ett cacheblock.

Dessutom finns det förfrågningar på busssidan. Dessa inkluderar:

- BusRd: När en läsmiss inträffar i en processors cache, skickar den en BusRd-begäran på bussen och förväntar sig att få cacheblocket i gengäld.

- BusRdX: När en skrivmiss inträffar i en processors cache, skickar den en BusRdX-begäran på bussen som returnerar cacheblocket och ogiltigförklarar blocket i andra processorers cache.

- BusUpgr: När det finns en skrivträff i en processors cache, skickar den en BusUpgr-begäran på bussen för att ogiltigförklara blocket i andra processorers cache.

- Spola: Begäran som indikerar att ett helt cacheblock skrivs tillbaka till minnet.

Statsövergångar:

-

Ogiltigt :

- På en PrRd utfärdas BusRd och ändras till Shared .

- På en PrWr utfärdas BusRdX och ändras till Modified .

- På en BusRd, BusRdX eller en BusUpgr förblir ett ogiltigt block Invalid .

-

Delad :

- På en PrRd förblir blocket i delat tillstånd.

- På en PrWr utfärdas BusUpgr och ändras till Modified .

- På en BusRd förblir blocket i delat tillstånd.

- På en BusRdX eller BusUpgr övergår blocket till Invalid .

-

Ändrad :

- På en PrRd eller PrWr förblir blocket i det modifierade tillståndet.

- På en BusRd spolas cacheblocket till bussen och tillståndet ändras till Shared .

- På en BusRdX spolas cacheblocket till bussen och tillståndet ändras till Invalid .

- En BusUpgr är inte möjlig. Observera att genom att vara i Modifierat tillstånd i en viss processor, måste ett cacheblock vara i Ogiltigt tillstånd i alla andra processorer, eftersom det Modifierade tillståndet är tillåtet i antingen ingen eller endast en processor. Detta förnekar effektivt möjligheten av en BusUpgr på bussen, vilket skulle kräva att detta block är i det delade tillståndet i en av processorerna som, som framgår av ovan, utfärdar en PrWr.

Användande

Detta protokoll liknar det som används i SGI 4D-maskinen.

Varianter

Moderna system använder varianter av MSI-protokollet för att minska mängden trafik i koherenssammankopplingen. MESI -protokollet lägger till ett "Exklusivt" tillstånd för att minska trafiken som orsakas av skrivningar av block som bara finns i en cache. MOSI -protokollet lägger till ett "ägt" tillstånd för att minska trafiken som orsakas av återskrivningar av block som läses av andra cachar. MOESI -protokollet gör båda dessa saker.