hyperSPARC

| Allmän information | |

|---|---|

| Lanserades | 1993 |

| Avvecklad | 1996 |

| Designad av | Ross teknologi |

| Prestanda | |

| Max. CPU klockfrekvens | 40 MHz till 200 MHz |

| Arkitektur och klassificering | |

| Instruktionsuppsättning | SPARC V8 |

| Fysiska specifikationer | |

| Kärnor |

|

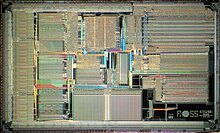

HyperSPARC , med kodnamnet "Pinnacle", är en mikroprocessor som implementerar SPARC version 8 instruction set architecture (ISA) utvecklad av Ross Technology för Cypress Semiconductor .

HyperSPARC introducerades 1993 och konkurrerade med Sun Microsystems SuperSPARC . Raju Vegesna var mikroarkitekten. HyperSPARC var Sun Microsystems främsta konkurrent i mitten av 1990-talet. När Fujitsu förvärvade Ross från Cypress ansågs hyperSPARC vara viktigare av sin nya ägare än SPARC64 som utvecklats av HAL Computer Systems , också ett Fujitsu dotterbolag, en uppfattning som delades med analytiker.

Beskrivning

HyperSPARC var en tvåvägs superskalär mikroprocessor. Den hade fyra exekveringsenheter: en heltalsenhet, en flyttalsenhet, en last/lagerenhet och en filialenhet. HyperSPARC:n har en instruktionscache på 8 KB, från vilken två instruktioner hämtades per cykel och avkodades. Avkodaren kunde inte avkoda nya instruktioner om de tidigare avkodade instruktionerna inte utfärdades till exekveringsenheterna.

Heltalsregisterfilen innehöll 136 register, som tillhandahåller åtta registerfönster , en funktion som definieras i SPARC ISA. Den hade två läsportar. Heltalsenheten hade en fyrstegspipeline , varav två steg lades till så att pipelinen skulle vara lika med alla icke-flytande-komma-pipelines. Heltalsmultiplicera och dividera, instruktioner som lades till i V8-versionen av SPARC-arkitekturen, hade 18 respektive 37 cyklers latens, och stoppade pipelinen tills de var färdiga.

Mikroprocessorn stödde multiprocessing på MBus -system.

Fysisk

HyperSPARC består av 1,2 miljoner transistorer. Den tillverkades av Cypress i deras 0,65 µm, tvålagers metall, komplementära metall-oxid-halvledare (CMOS) process. Senare iterationer av hyperSPARC har fler transistorer på grund av nya funktioner och portades till nyare processer. De tillverkades av Fujitsu , förutom den sista iterationen, som tillverkades av NEC .

Förpackning

HyperSPARC var en multi-chip design. Den var förpackad i en keramisk multichipmodul (MCM) med en pingrid array (PGA).

Chipset

HyperSPARC använde Cypress SparcSet-chipset som introducerades i slutet av juli 1992. Det utvecklades av Santa Clara, Kaliforniens startup Nimbus Technologies, Inc. för Cypress, som tillverkade designen. SparcSet var också kompatibel med andra SPARC-mikroprocessorer.

- Levine, Bernard (11 april 1994). "MCM-förespråkare lockar blivande användare" . Elektroniska nyheter .

- Holden, Daniel (15 februari 1993). "Cypress, Sun: HyperSPARC hypertoni" . Elektroniska nyheter .

- Holden, Daniel (15 mars 1993). "HyperSparc synar union med Intel på P6-processor" . Elektroniska nyheter .

- Holden, Daniel (19 april 1993). "HyperSPARC går långsamt med Sun Micro" . Elektroniska nyheter .

- Shen, John Paul och Lipasti, Mikko H. (2004). Modern processordesign . McGraw-Hill Professional.

Vidare läsning

- "Ross förhandsgranskar Pinnacle SPARC Design". (25 mars 1992). Microprocessor Report , vol. 6, nr. 4.

- "TI och Cypress/Ross slåss om SPARC-ledarskap". (27 maj 1992). Microprocessor Report , vol. 6, nr. 7.

- "Ross skickar äntligen HyperSPARC". (15 november 1993). Microprocessor Report , vol. 7, nr. 15.

- "Förbättrad HyperSparc utmanar UltraSparc". (4 december 1995). Microprocessor Report , vol. 9, nr. 16.