Händelsetimer med hög precision

High Precision Event Timer ( HPET ) är en hårdvarutimer som är tillgänglig i moderna x86-kompatibla persondatorer . Jämfört med äldre typer av timers tillgängliga i x86-arkitekturen tillåter HPET effektivare bearbetning av mycket tidskänsliga applikationer, såsom multimediauppspelning och OS- uppgiftsbyte . Den utvecklades gemensamt av Intel och Microsoft och har inkorporerats i PC-chipset sedan 2005. Tidigare kallad av Intel som en Multimedia Timer , termen HPET valdes för att undvika förväxling med programvarans multimediatimer som introducerades i MultiMedia Extensions till Windows 3.0 .

Äldre operativsystem som inte stöder en HPET-hårdvaruenhet kan bara använda äldre tidtagningsfaciliteter, såsom den programmerbara intervalltimern (PIT) eller realtidsklockan (RTC). Windows XP , när det är utrustat med det senaste hårdvaruabstraktionslagret (HAL), kan också använda processorns tidsstämpelräknare (TSC) eller ACPI Power Management Timer (ACPI PMTIMER), tillsammans med RTC för att tillhandahålla operativsystemfunktioner som skulle, i senare Windows-versioner, tillhandahålls av HPET-hårdvaran. Förvirrande nog citerar sådana Windows XP-system "HPET"-anslutning i drivrutinshanteraren även om Intel HPET-enheten inte används.

Funktioner

Ett HPET-chip består av en 64-bitars uppräknare (huvudräknare) som räknar med en frekvens på minst 10 MHz, och en uppsättning (minst tre, upp till 256) komparatorer. Dessa komparatorer är 32- eller 64-bitars breda. HPET programmeras via ett minnesmappat I/O- fönster som är upptäckbart via ACPI . HPET-kretsen i moderna datorer är integrerad i Southbridge-chippet .

Varje komparator kan generera ett avbrott när de minst signifikanta bitarna är lika med motsvarande bitar av 64-bitars huvudräknarevärde. Komparatorerna kan sättas i en-shot-mod eller periodisk mod, med åtminstone en komparator som stöder periodisk mod och alla stöder en-shot-mod. I engångsläge avfyrar komparatorn ett avbrott en gång när huvudräknaren når det värde som är lagrat i komparatorns register, medan i det periodiska läget genereras avbrotten med specificerade intervall.

Komparatorer kan drivas av operativsystemet, t.ex. för att tillhandahålla en timer per CPU för schemaläggning, eller av applikationer.

Ansökningar

HPET kan producera periodiska avbrott med en mycket högre upplösning än RTC och används ofta för att synkronisera multimediaströmmar, vilket ger smidig uppspelning och minskar behovet av att använda andra tidsstämpelberäkningar såsom en x86-baserad CPU:s RDTSC - instruktion . Detta ger förbättrad effektivitet, eftersom CPU:n inte behöver slösa cykler för att kompensera för den låga upplösningen av timers, och möjliggör mer aggressiv användning av vilolägen , vilket minskar strömförbrukningen. Utöver efterfrågan på applikationsnivå för högprecisionsklockor, finns det fördelar på OS-nivå i schemaläggaren och genom tillgången till en stabil klockbas för system med flera processorer .

Jämförelse med föregångare

HPET är tänkt att komplettera och ersätta den programmerbara intervalltimern 8254 och RTC:s periodiska avbrottsfunktion. Jämfört med dessa äldre timerkretsar har HPET högre frekvens och bredare 64-bitarsräknare (även om de kan drivas i 32-bitarsläge).

HPET-specifikationen definierar inte timerfrekvensen, den kräver endast ett minimum av 10 MHz; den faktiska frekvensen tillhandahålls till operativsystemet av ett hårdvaruregister som anger antalet femtosekunder per period (med en övre gräns på 100 000 000 fs ). Ett populärt värde är 14,3 18 MHz, 12 gånger standardfrekvensen 8254 på 1,193 18 MHz.

Medan 8254 och RTC kan sättas i ett HPET-liknande one-shot-läge, är installationsprocessen så långsam att deras one-shot-läge inte används i praktiken för uppgifter som kräver exakt schemaläggning. Istället används 8254 och RTC vanligtvis i periodiskt läge med ett mycket litet tidsintervall. Till exempel, om en applikation behöver utföra flera korta (några millisekunder, kanske) väntetider, är det bättre att ha en periodisk timer igång konstant med en period på 1 ms på grund av den höga installationskostnaden för en 8254 eller RTC one-shot timer. Detta orsakar ett avbrott vid varje millisekund även om applikationen behöver utföra verkligt arbete mer sällan. Med HPET kan de extra avbrotten undvikas, eftersom installationskostnaden för en HPET one-shot timer är betydligt mindre.

Användning och kompatibilitet

Operativsystem designade innan HPET existerade kan inte använda HPET, så de använder andra timerfunktioner. Nyare operativsystem tenderar att kunna använda antingen. En del hårdvara har båda. Faktum är att de flesta nuvarande southbridge-chips har äldre instanser av PIT, PIC, Advanced Programmable Interrupt Controller (APIC) och RTC-enheter inbyggda i deras kisel oavsett om de används av operativsystemet eller inte, vilket hjälper mycket moderna datorer att köra äldre operativsystem .

Följande operativsystem är kända för att inte kunna använda HPET: Windows XP SP1, och tidigare Windows- versioner, Linux -kärnor före 2.6.

Följande operativsystem är kända för att kunna använda HPET: Windows XP SP3, Windows Server 2003 SP2 , Windows Server 2008 , Windows Server 2008 R2 , Windows Vista , Windows 7 , x86-baserade versioner av OS X , Linux -operativsystem som använder 2.6 kärna (eller senare), FreeBSD och OpenSolaris . [ citat behövs ]

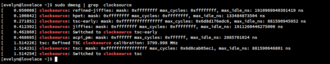

Linuxkärnan kan också använda HPET som sin klockkälla . Dokumentationen för Red Hat MRG version 2 säger att TSC är den föredragna klockkällan på grund av dess mycket lägre overhead, men den använder HPET som reserv. Ett riktmärke i den miljön för 10 miljoner händelser visade att TSC tog cirka 0,6 sekunder, HPET tog drygt 12 sekunder och ACPI Power Management Timer tog cirka 24 sekunder.

Under 2019 beslutades det att svartlista HPET i nyare Linux-kärnor när de körs på vissa Intel-processorer ( Coffee Lake ) på grund av dess instabilitet.

Problem

HPET är en kontinuerligt pågående timer som räknar uppåt, inte en engångsenhet som räknar ner till noll, orsakar ett avbrott och sedan stannar. Eftersom HPET jämför det faktiska timervärdet och det programmerade målvärdet på likhet snarare än "större eller lika", kan avbrott missas om måltiden redan har passerat när komparatorvärdet skrivs in i chipets register. I ett sådant fall missas inte bara det avsedda avbrottet, utan sätts faktiskt långt in i framtiden (cirka 2 32 eller 2 64 punkter). I närvaro av icke-maskerbara avbrott (som ett systemhanteringsavbrott (SMI)) som inte har en hård övre gräns för sin körningstid, kräver detta tävlingstillstånd tidskrävande omkontroller av timern efter installationen och är svårt att undvika helt. Svårigheterna förvärras om komparatorvärdet inte synkroniseras med timern omedelbart, utan fördröjs med en eller två markeringar, som vissa chipset gör.

Förutom att nämna tävlingsvillkoret som diskuterats ovan, listar ett VMware- dokument även några andra nackdelar: "Specifikationen kräver inte att timern är särskilt finkornig, har låg drift eller är snabb att läsa. Vissa typiska implementeringar kör räknaren kl. cirka 18 MHz och kräver ungefär samma tid (1–2 μs) för att läsa HPET som med ACPI-timern. Implementationer har observerats där periodregistret är avstängt med 800 delar per miljon eller mer."