Fyrfasig logik

Fyrfaslogik är en typ av och designmetodik för dynamisk logik . Det gjorde det möjligt för icke-specialistingenjörer att designa ganska komplexa IC:er , med antingen PMOS- eller NMOS -processer. Den använder en slags 4-fas klocksignal .

Historia

RK "Bob" Booher, ingenjör på Autonetics , uppfann fyrfaslogik och förmedlade idén till Frank Wanlass på Fairchild Semiconductor ; Wanlass främjade denna logiska form vid General Instrument Microelectronics Division. Booher gjorde det första fungerande fyrfaschippet, Autonetics DDA-integratorn , under februari 1966; han designade senare flera chips för och byggde Autonetics D200 luftburna dator med denna teknik.

I april 1967 publicerade Joel Karp och Elizabeth de Atley en artikel "Use four-phase MOS IC logic" i tidningen Electronic Design . Samma år publicerade Cohen, Rubenstein och Wanlass "MTOS fyrfas klocksystem." Wanlass hade varit chef för forskning och ingenjörskonst vid General Instrument Microelectronics Division i New York sedan han lämnade Fairchild Semiconductor 1964.

Lee Boysel , en lärjunge till Wanlass och en designer på Fairchild Semiconductor , och senare grundare av Four-Phase Systems , höll ett "sena nyheter" föredrag om en fyrfas 8-bitars adderare i oktober 1967 vid International Electron Devices möte. JL Seely, chef för MOS Operations vid General Instrument Microelectronics Division, skrev också om fyrfaslogik i slutet av 1967.

1968 publicerade Boysel en artikel "Adder on a Chip: LSI Helps Reduce Cost of Small Machine" i tidningen Electronics ; Fyrfaspapper från YT Yen dyker också upp det året. Andra tidningar följde inom kort.

Boysel påminner om att fyrfas dynamisk logik gjorde det möjligt för honom att uppnå 10X packningsdensiteten, 10X hastigheten och 1/10 kraften, jämfört med andra MOS-tekniker som användes vid den tiden (metal-gate saturated-load PMOS logic) , med hjälp av den första generationens MOS-process på Fairchild.

Strukturera

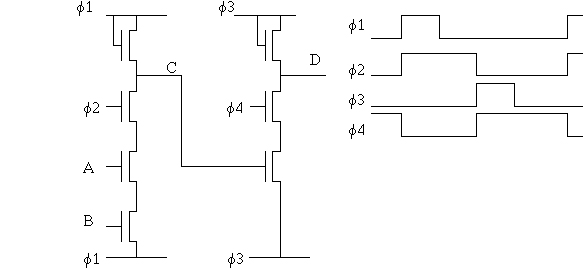

Det finns i princip två typer av logikgrind – en "1"-grind och en "3"-grind. Dessa skiljer sig endast i klockfaserna som används för att driva dem. En grind kan ha vilken logisk funktion som helst; sålunda har potentiellt varje grind en skräddarsydd layout. Ett exempel på 2-ingångs NAND 1-grind och en inverter 3-grind, tillsammans med deras klockfaser (exemplet använder NMOS-transistorer), visas nedan:

ϕ1- och ϕ3-klockorna måste vara icke-överlappande, liksom ϕ2- och ϕ4-klockorna. Med tanke på 1-grinden, under ϕ1 klockhögtid (även känd som förladdningstiden ) förladdar utgången C upp till V(ϕ1)−Vth, där Vth representerar tröskelvärdet för förladdningstransistorn. Under nästa kvartsklockcykel (sampeltiden ) , när ϕ1 är låg och ϕ2 är hög, förblir C antingen hög (om A eller B är låg) eller så urladdas C låg (om A och B är höga).

A- och B-ingångarna måste vara stabila under denna samplingstid. Utgången C blir giltig under denna tid – och därför kan en 1-gate-utgång inte driva ytterligare 1-gates ingångar. Därför måste 1 grindar mata 3 grindar och de i sin tur måste mata 1 grindar.

En sak till är användbar – 2 och 4 grindar. En 2 gate förladdar på ϕ1 och samplingar på ϕ3:

och en 4 gate förladdningar på ϕ3 och samplingar på ϕ1.

Gatesammankopplingsregler är: 1 grindar kan driva 2 grindar och/eller 3 grindar; 2 grindar kan driva endast 3 grindar, 3 grindar kan driva 4 grindar och/eller 1 grindar, 4 grindar kan driva endast 1 grindar:

Användande

Fyrfaslogik fungerar bra; i synnerhet finns det inga rasrisker eftersom varje kombinationslogikgrind inkluderar ett register. Det är värt att notera att layouten inte kräver bussning av några strömförsörjningar – endast klocklinjer bussas. Dessutom, eftersom designtekniken är kvotlös (jfr statisk logik ), kan många konstruktioner använda minimistorlekstransistorer.

Det finns några svårigheter:

- Grindutgången är dynamisk. Detta innebär att dess tillstånd hålls på kapacitans vid gate-utgången. Men utgångsspåret kan korsa klocklinjer och andra grindutgångar, som alla kan ändra laddningen på kondensatorn. För att grindens utspänning förblir på någon säker 0- eller 1-nivå under cykeln måste storleken på förändringen beräknas och, om nödvändigt, måste ytterligare (diffusions)kapacitans läggas till utgångsnoden.

- För en given matningsspänning, process och klockfrekvens måste konstruktören göra några beräkningar så att layoutingenjörerna i sin tur kan göra sina beräkningar för att räkna ut den "bulk-up" kapacitans som behövs för varje grind. En grind med mycket kapacitansbelastning kan behöva större än minsta ingångstransistorer (för att lasten ska kunna laddas ur i tid). Detta ökar i sin tur belastningen på grindarna som driver den grindens ingångar. Så det kan hända, särskilt i högfrekventa konstruktioner, att grindens dimensionering fortsätter att öka om hastighetsmålet är för aggressivt.

Den första elektroniska räknaren som byggdes med storskaliga integrerade kretsar (LSI), Sharp QT-8D från 1969, använde 4-fas logik som tillverkades av Rockwell International eftersom Japan ännu inte hade LSI-tekniken för att göra det på hemmaplan. 4-fas logik övervägdes också för användning i Intel 4004 , men bara Rockwell hade designverktygen och expertis för att göra storskaliga 4-fas IC:er vid den tiden så Intel bestämde sig för 2-fas dynamisk logik istället.

Evolution

Med tillkomsten av CMOS kunde förladdningstransistorn ändras till att vara komplementet till den logiska transistortypen, vilket gör att grindens utgång kan laddas snabbt hela vägen upp till den höga nivån på klocklinjen, vilket förbättrar hastigheten, signalsvängningen , strömförbrukning och brusmarginal. Denna teknik används i dominologik .